# A Quantitative Performance Evaluation of SCI Memory Hierarchies

Roberto A Hexsel

Ph.D.

University of Edinburgh

1994

#### Abstract

The Scalable Coherent Interface (SCI) is an IEEE standard that defines a hard-ware platform for scalable shared-memory multiprocessors. SCI consists of three parts. The first is a set of physical interfaces that defines board sizes, wiring and network clock rates. The second is a communication protocol based on unidirectional point to point links. The third defines a cache coherence protocol based on a full directory that is distributed amongst the cache and memory modules. The cache controllers keep track of the copies of a given datum by maintaining them in a doubly linked list. SCI can scale up to 65520 nodes.

This dissertation contains a quantitative performance evaluation of an SCI-connected multiprocessor that assesses both the communication and cache coherence subsystems. The simulator is driven by reference streams generated as a by-product of the execution of "real" programs. The workload consists of three programs from the SPLASH suite and three parallel loops.

The simplest topology supported by SCI is the ring. It was found that, for the hardware and software simulated, the largest efficient ring size is between eight and sixteen nodes and that raw network bandwidth seen by processing elements is limited at about 80Mbytes/s. This is because the network saturates when link traffic reaches 600–700Mbytes/s. These levels of link traffic only occur for two poorly designed programs. The other four programs generate low traffic and their execution speed is *not* limited by interconnect *nor* cache coherence protocol. An analytical model of the multiprocessor is used to assess the cost of some frequently occurring cache coherence protocol operations. In order to build large systems, networks more sophisticated than rings must be used. The performance of SCI meshes and cubes is evaluated for systems of up to 64 nodes. As with rings, processor throughput is also limited by link traffic for the same two poorly designed programs. Cubes are 10–15% faster than meshes for programs that generate high levels of network traffic. Otherwise, the differences are negligible. No significant relationship between cache size and network dimensionality was found.

#### Acknowledgements

This dissertation is one of the products of my living in Scotland. It was a period of much discovery, both technically and personally. On the personal side, I lived there long enough to become well acquainted with British culture and politics. Some of the good memories I will keep are from many hours spent with BBC Radio 4, BBC 1 and 2, Channel 4, The Edinburgh Filmhouse, The Cameo Cinema, The Queen's Hall, The Royal Sheakespeare Company. Through these media, I met the Bard and Handel, Inspectors Taggart and Frost, Jeremy Paxman and John Pilger, Marina Warner and Glenys Kinnock, Noam Chomsky and Edward Said, Dennis Skinner and Tony Benn, Prime Minister Question Time and Spitting Image, Peter Greenaway and a wealth of European cinema. Along with many others, these people, their work and the institutions they work for became an important element of my thinking. Being in exile is not easy but it can be an extremely enriching experience. It was for me.

Many people took part, directly or indirectly, in the work that is reported here. Some were related to me in a professional capacity, some helped by just being there. I would like to express my gratitude to them all.

The Coordenadoria de Aperfeiçoamento de Pessoal de Nível Superior (CAPES), Ministério da Educação, Brazil, awarded the scholarship that made possible my coming to Britain.

I would like to thank the people at the Department of Computer Science for making easy my life and endeavours as a graduate student. In particular, I am grateful to Angela, Chris (cc), Eleanor, George, Jenny, John (jhb), Murray, Paul, Sam and Todd. I would also like to thank all the people who put up with my simulations hogging the compute servers and/or their workstations.

Dave Gustavson, the chairman of the IEEE-SCI working group, provided useful coments on a paper about SCI rings that evolved into Chapter 4. He kept insisting, thankfully, that SCI=rings is not true!

Nigel Topham was my supervisor and I am indebted to him for the opportunity to work on Computer Architecture. I am also indebted to Nigel for his guidance and support. Had I followed his advice more closely on a few occasions, much time and grief would have been saved. Stuart Anderson was my second supervisor and I thank him for being there during the mid-summer crises.

My parents offered much needed support and encouragement. Without their financial support in the later stages of this work, it would not have been completed.

I must mention the hillwalkers, with whom I discovered much beauty and wilderness in Scotland. Fábio, Kees, and Paul got me started. During the addiction stage we endured mist, rain, gales, sleet and snow, and occasionally, breathtaking views from the tops and ridges of many Munros and Corbetts. In this period were also participants Brian, Irene, Jessy, Olivier, Peter, and many others. The time we spent together on the hills and glens will be sorely missed.

I am also grateful to the house- and office-mates with whom I shared the many frustrations and few delights of being a foreign graduate student: Claudio, Davide, Deena, Li Guo and Matthew. Also, the friends who were neither office/house mates nor hillwalkers: Alice & Alberto, Cláudia, Jane & Stephen, Laureance, Mandy and Margareth. I am grateful to Joaquin for the many long discussions we had, which helped me to stay within reasonable levels of sanity.

Many people kept writing to me, in the forlorn hope of a reply. Their letters kept me in a healthy state of homesickness. Bila & Conrado, Dina, Edela, Guga and Lina, kept a constant and most welcome stream of letters flowing during these years.

Most of all, I thank Helena, for her endurance, love and wee Julia.

#### **Declaration**

I declare that this Thesis was written by myself and that the work it describes is my own, except where stated in the text.

> Roberto André Hexsel 22nd of September 1994.

# Table of Contents

| 1.                               | Intr                          | oducti                  | on                                       | 1  |

|----------------------------------|-------------------------------|-------------------------|------------------------------------------|----|

| 2.                               | Shared Memory Multiprocessors |                         |                                          |    |

|                                  | 2.1                           | Interco                 | onnection Networks                       | 6  |

|                                  | 2.2                           | Shared                  | l Memory Implementations                 | 10 |

|                                  |                               | 2.2.1                   | Cache Memories                           | 10 |

|                                  |                               | 2.2.2                   | Multiprocessor Cache Coherency           | 12 |

|                                  |                               | 2.2.3                   | Ring Based Shared-Memory Multiprocessors | 15 |

|                                  | 2.3                           | The So                  | calable Coherent Interface               | 16 |

|                                  |                               | 2.3.1                   | SCI Communication Protocol               | 17 |

|                                  |                               | 2.3.2                   | SCI Cache Coherence Protocol             | 18 |

|                                  |                               | 2.3.3                   | Related Work                             | 21 |

| 3.                               | The                           | Archi                   | tecture Simulator                        | 24 |

|                                  | 3.1                           | Simula                  | ation Methodology                        | 24 |

| 3.2 The Simulated Multiprocessor |                               | imulated Multiprocessor | 27                                       |    |

|                                  |                               | 3.2.1                   | Processors and Memory Hierarchy          | 27 |

|                                  |                               | 3.2.2                   | The Simulation Model of SCI Rings        | 30 |

|                                  | 3.3                           | The W                   | Vorkload                                 | 32 |

|                                  |                               | 3.3.1                   | SPLASH Programs                          | 33 |

|                                  |                               | 3.3.2                   | Parallel Loops                           | 34 |

|                                  |                               | 3.3.3                   | Data Set Sizes                           | 36 |

|                                  | 3.4                           | Accura                  | acy of the Simulation Results            | 38 |

Table of Contents iv

| 4.         | The                                           | Perfo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rmance of SCI Rings                                | <b>4</b> 0                                               |

|------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|

|            | 4.1                                           | Perfor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | mance Metrics                                      | 40                                                       |

|            | 4.2                                           | Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | and Ring Design                                    | 42                                                       |

|            |                                               | 4.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Design Space                                       | 42                                                       |

|            |                                               | 4.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Characterising the Workload                        | 43                                                       |

|            |                                               | 4.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cache Size and Cache Access Latency                | 48                                                       |

|            |                                               | 4.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Processor Clock Speed                              | 53                                                       |

|            | 4.3                                           | Throu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ghput and Latency                                  | 54                                                       |

|            | 4.4                                           | Other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ring-based Systems                                 | 59                                                       |

|            |                                               | 4.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Comparing DASH and SCI                             | 59                                                       |

| <b>5</b> . | A N                                           | Iodel (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | of the SCI-connected Multiprocessor                | 67                                                       |

|            | 5.1                                           | The A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nalytical Model                                    | 67                                                       |

|            | 5.2                                           | Costin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | g Sharing-lists and Conflict Misses                | 73                                                       |

|            |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                                          |

| 6.         | The                                           | Perfo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rmance of Meshes and Cubes                         | <b>7</b> 8                                               |

| 6.         | <b>The</b> 6.1                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rmance of Meshes and Cubes imulated Multiprocessor |                                                          |

| 6.         |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    | 78                                                       |

| 6.         |                                               | The S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | imulated Multiprocessor                            | 78<br>79                                                 |

| 6.         |                                               | The Sa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Routing                                            | 78<br>79<br>80                                           |

| 6.         | 6.1                                           | The Second of th | Routing                                            | 78<br>79<br>80                                           |

| 6.         | 6.1                                           | The Si 6.1.1 6.1.2 SCI M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Routing                                            | 78<br>79<br>80<br>81                                     |

| 6.         | 6.1                                           | The Si<br>6.1.1<br>6.1.2<br>SCI M<br>6.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Routing                                            | 78<br>79<br>80<br>81<br>81                               |

| 6.         | 6.1                                           | The Si 6.1.1 6.1.2 SCI M 6.2.1 6.2.2 6.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Routing                                            | 78<br>79<br>80<br>81<br>81<br>83                         |

| 6.         | 6.1                                           | The Si 6.1.1 6.1.2 SCI M 6.2.1 6.2.2 6.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Routing                                            | 78<br>79<br>80<br>81<br>81<br>83                         |

| 6.         | 6.1                                           | The Si 6.1.1 6.1.2 SCI M 6.2.1 6.2.2 6.2.3 SCI C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Routing                                            | 78<br>79<br>80<br>81<br>81<br>83<br>85<br>89             |

| 6.         | 6.1                                           | The Si 6.1.1 6.1.2 SCI M 6.2.1 6.2.2 6.2.3 SCI C 6.3.1 6.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Routing                                            | 78<br>79<br>80<br>81<br>81<br>83<br>85<br>89             |

| 6.         | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul> | The Si 6.1.1 6.1.2 SCI M 6.2.1 6.2.2 6.2.3 SCI C 6.3.1 6.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Routing                                            | 78<br>79<br>80<br>81<br>81<br>83<br>85<br>89<br>92<br>95 |

Table of Contents v

| 7. | Con              | clusio | n                                                    | 101 |  |  |  |

|----|------------------|--------|------------------------------------------------------|-----|--|--|--|

| Α. | Performance Data |        |                                                      |     |  |  |  |

|    | A.1              | SCI R  | ings                                                 | 115 |  |  |  |

|    |                  | A.1.1  | chol() – DASH Parameters                             | 115 |  |  |  |

|    |                  | A.1.2  | $mp3d()-DASH\ Parameters\ \dots\dots\dots\dots\dots$ | 116 |  |  |  |

|    |                  | A.1.3  | water() – DASH Parameters                            | 117 |  |  |  |

|    |                  | A.1.4  | chol()                                               | 118 |  |  |  |

|    |                  | A.1.5  | mp3d()                                               | 121 |  |  |  |

|    |                  | A.1.6  | water()                                              | 124 |  |  |  |

|    |                  | A.1.7  | ge()                                                 | 127 |  |  |  |

|    |                  | A.1.8  | mmult()                                              | 130 |  |  |  |

|    |                  | A.1.9  | paths()                                              | 133 |  |  |  |

|    | A.2              | SCI M  | leshes                                               | 136 |  |  |  |

|    |                  | A.2.1  | chol()                                               | 136 |  |  |  |

|    |                  | A.2.2  | mp3d()                                               | 137 |  |  |  |

|    |                  | A.2.3  | water()                                              | 138 |  |  |  |

|    |                  | A.2.4  | ge()                                                 | 139 |  |  |  |

|    |                  | A.2.5  | mmult()                                              | 140 |  |  |  |

|    |                  | A.2.6  | paths()                                              | 141 |  |  |  |

|    | A.3              | SCI C  | ubes                                                 | 143 |  |  |  |

|    |                  | A.3.1  | chol()                                               | 143 |  |  |  |

|    |                  | A.3.2  | mp3d()                                               | 143 |  |  |  |

|    |                  | A.3.3  | water()                                              | 144 |  |  |  |

|    |                  |        | ge()                                                 |     |  |  |  |

|    |                  | A.3.5  | mmult()                                              | 146 |  |  |  |

|    |                  | A.3.6  | paths()                                              | 147 |  |  |  |

# List of Figures

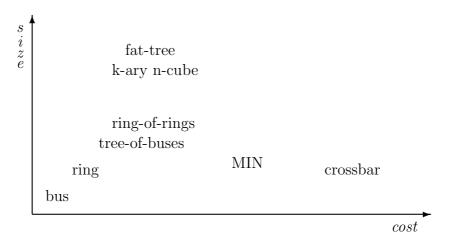

| 2.1  | Interconnection networks: network size <i>versus</i> cost                                     | 6  |

|------|-----------------------------------------------------------------------------------------------|----|

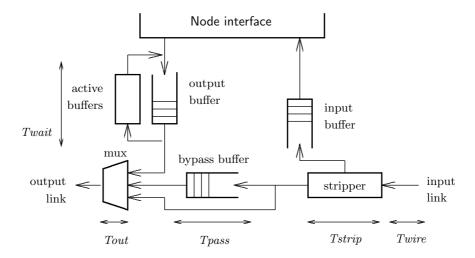

| 2.2  | SCI link interface                                                                            | 18 |

| 2.3  | Sharing-list setup                                                                            | 19 |

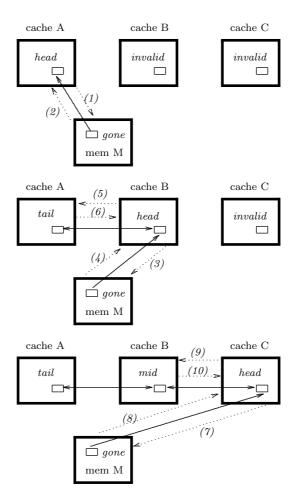

| 2.4  | Sharing-list purge sequence                                                                   | 20 |

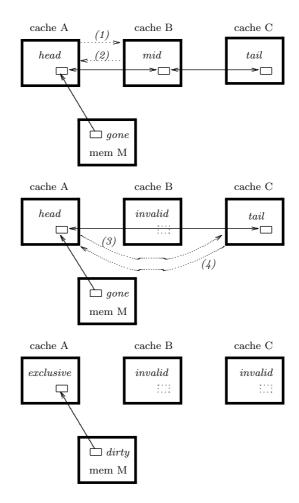

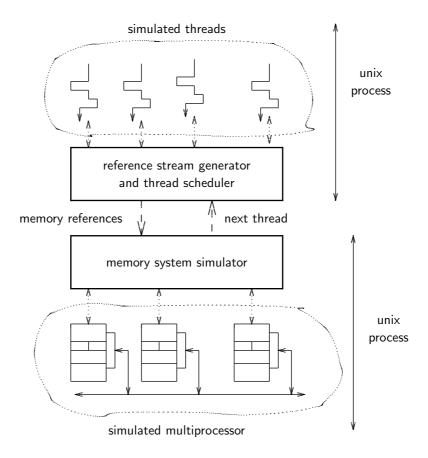

| 3.1  | Simulation environment                                                                        | 26 |

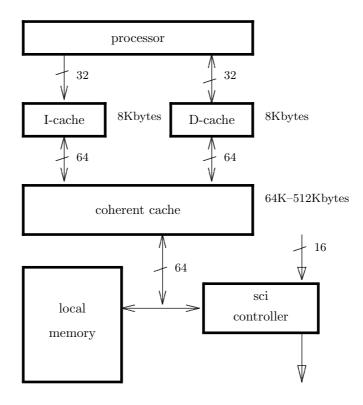

| 3.2  | Architecture of the processing nodes                                                          | 27 |

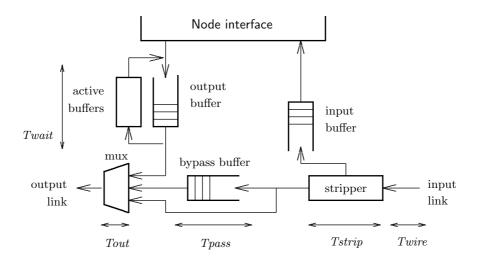

| 3.3  | SCI link interface                                                                            | 30 |

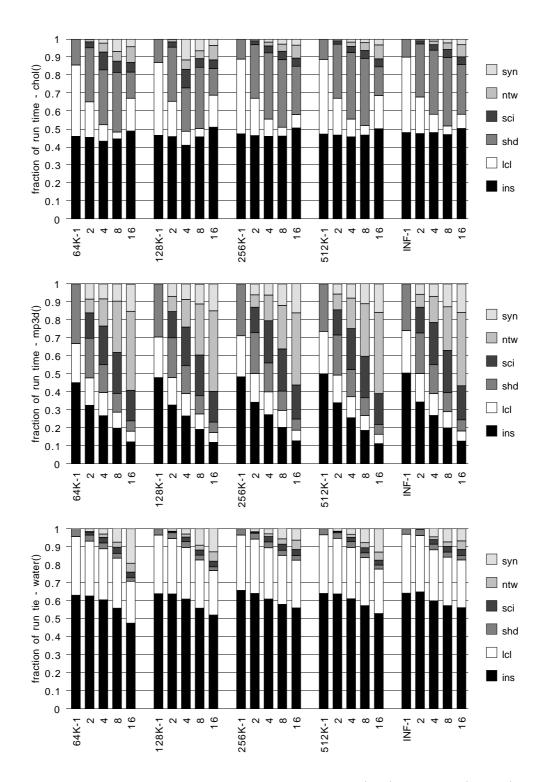

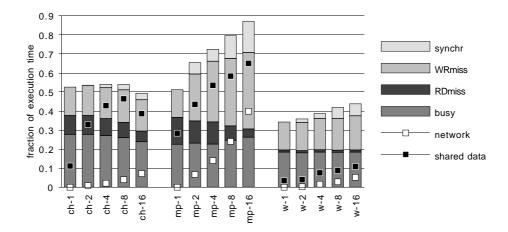

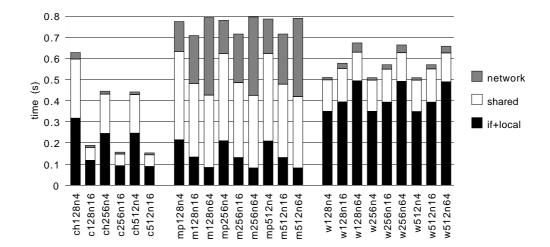

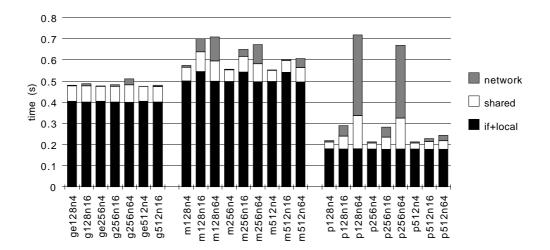

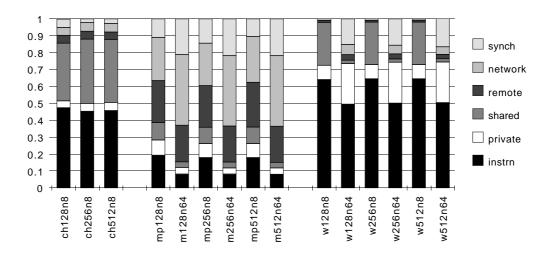

| 4.1  | Execution time breakdown for chol(), mp3d() and water()                                       | 45 |

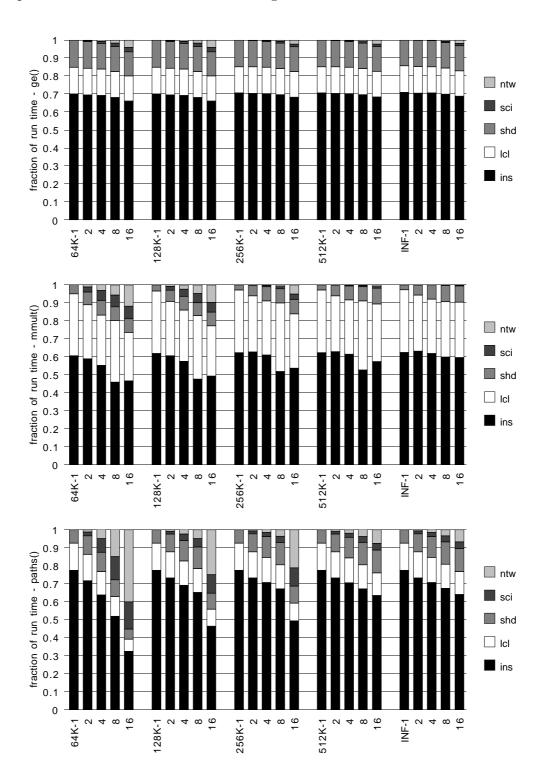

| 4.2  | Execution time breakdown for ge(), mmult() and paths()                                        | 46 |

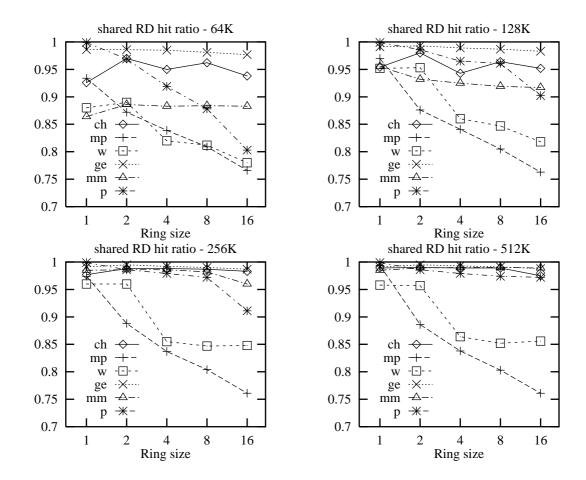

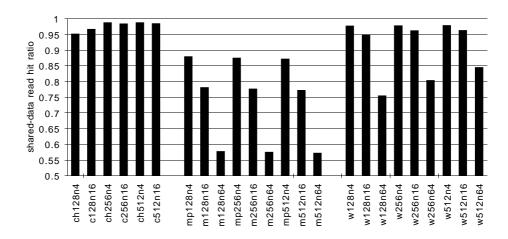

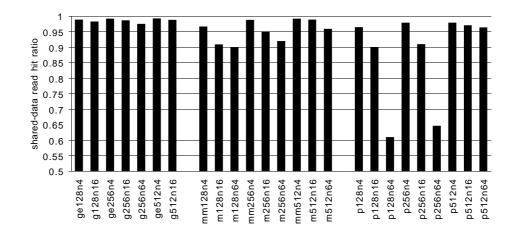

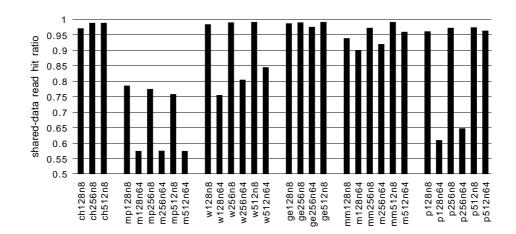

| 4.3  | Shared-data read hit ratios for 64K, 128K, 256K and 512Kbytes coherent caches                 | 48 |

| 4.4  | Execution time as a function of cache size, for chol(), mp3d() and water()                    | 51 |

| 4.5  | Execution time as a function of cache size, for ge(), mmult() and paths()                     | 52 |

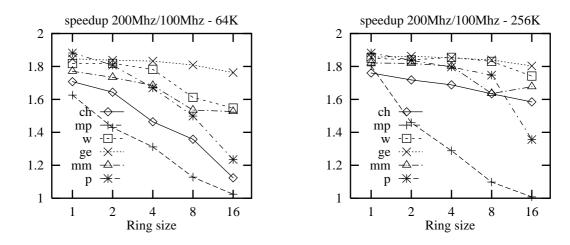

| 4.6  | Speedup achieved by doubling processor clock frequency, with cache sizes of 64K and 256Kbytes | 53 |

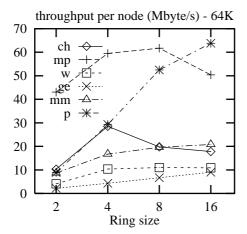

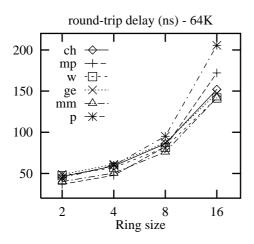

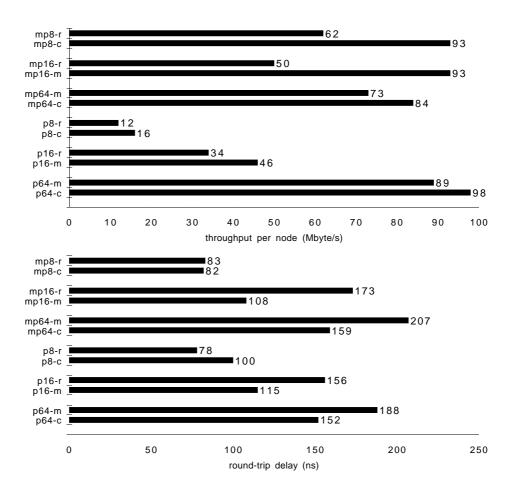

| 4.7  | Throughput per node, coherent cache sizes of $64\mathrm{K}$ and $256\mathrm{K}$ bytes         | 54 |

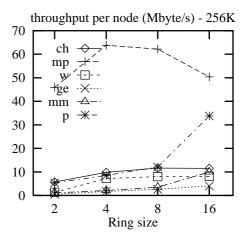

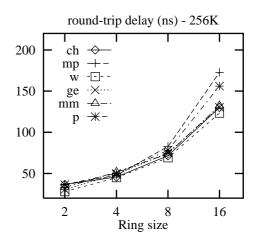

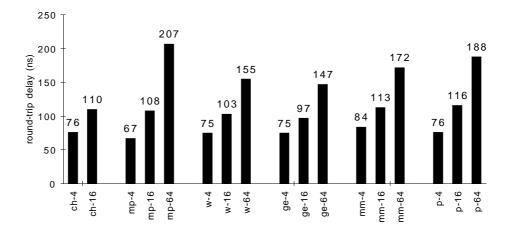

| 4.8  | Average round-trip delay, with cache sizes of 64K and 256Kbytes                               | 55 |

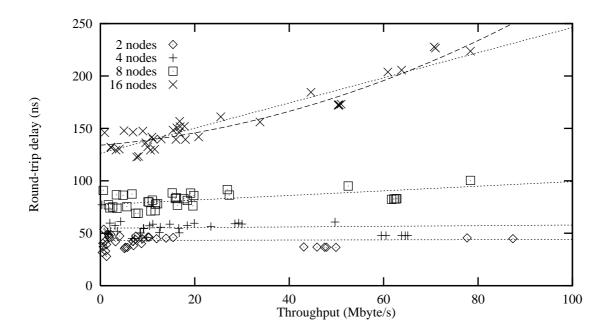

| 4.9  | Latency <i>versus</i> throughput on 2-, 4-, 8- and 16-node rings                              | 56 |

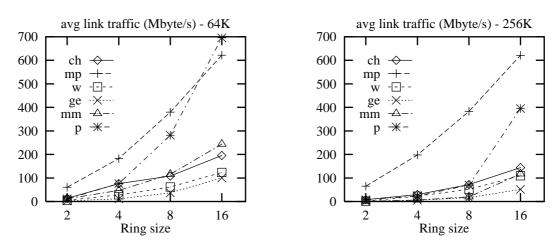

| 4.10 | Traffic per link, for cache sizes of 64KK and 256Kbytes                                       | 57 |

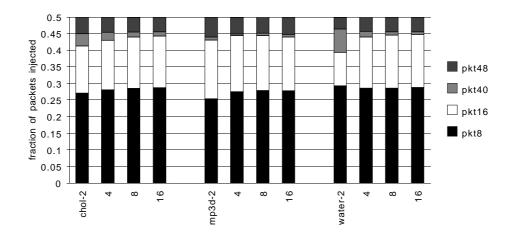

| 4.11 | Distribution of packet sizes for 256Kbytes caches                                             | 58 |

List of Figures vii

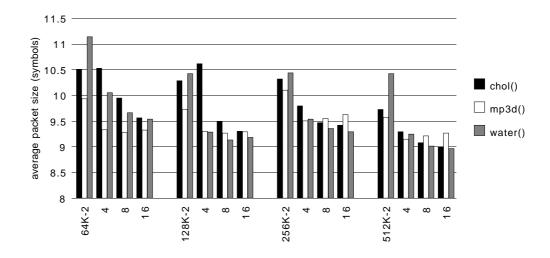

| 4. | 12 | Average packet size for 64K. 128K, 256K and 512Kbytes caches                                                  | 58 |

|----|----|---------------------------------------------------------------------------------------------------------------|----|

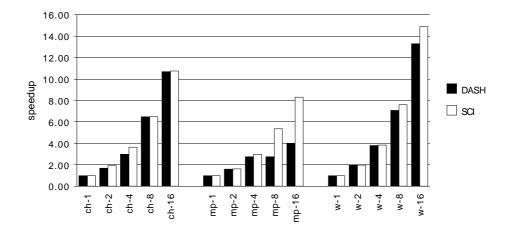

| 4. | 13 | Speedup plots for chol(), mp3d() and water()                                                                  | 62 |

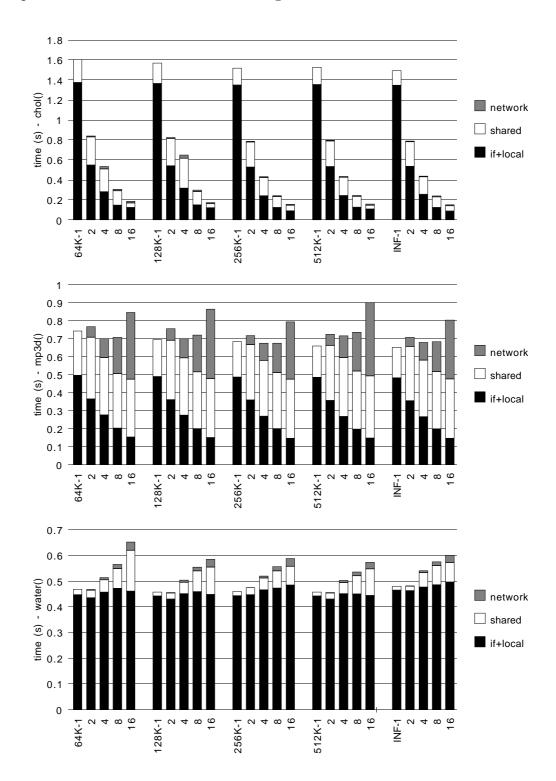

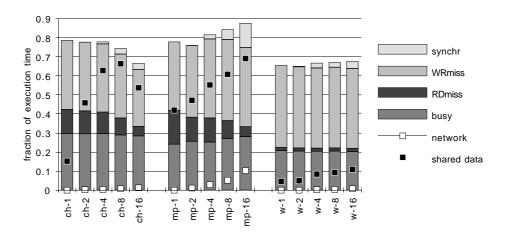

| 4. | 14 | Execution time breakdown for chol(), mp3d() and water()                                                       | 63 |

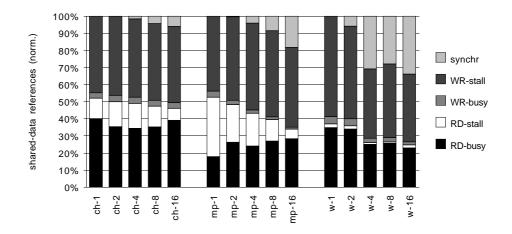

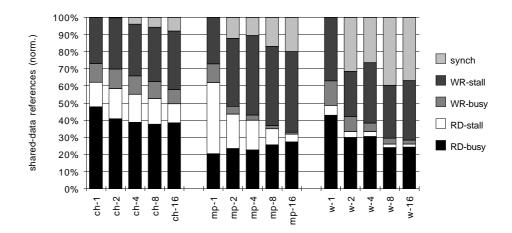

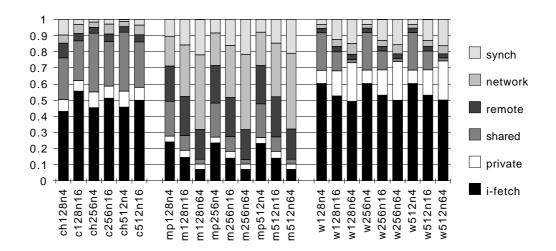

| 4. | 15 | Normalised execution time breakdown for chol() mp3d() and water(), for shared data references                 | 64 |

| 4. | 16 | Execution time breakdown for chol(), mp3d() and water() - 100MHz clock                                        | 65 |

| 4. | 17 | Normalised execution time breakdown for chol(), mp3d() and water(), for shared-data references — 100MHz clock | 65 |

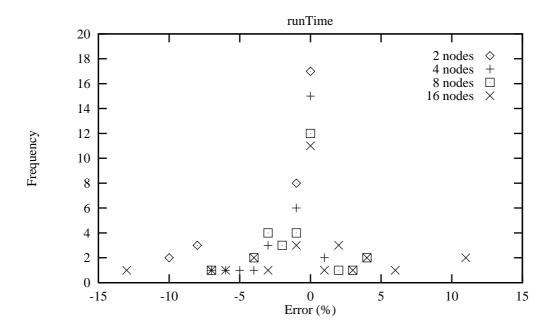

| 5. | 1  | Distribution of error in the model predictions when compared to the simulation result                         | 73 |

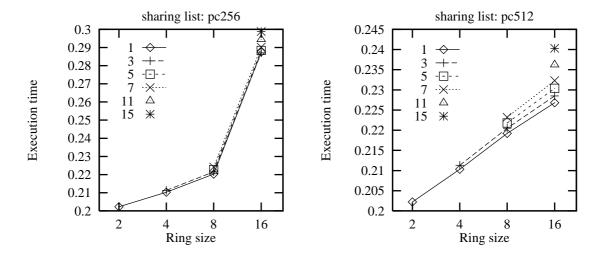

| 5. | 2  | Effect of long sharing lists on the performance of paths() with 256K and 512Kbytes caches                     | 74 |

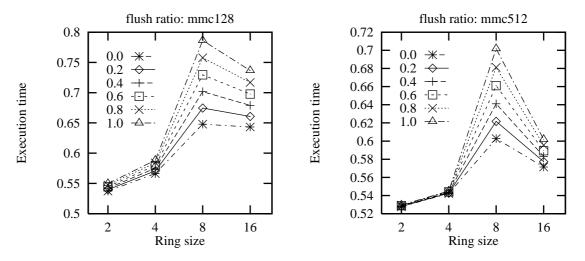

| 5. | 3  | Effect of conflict misses on the performance of mmult() with 128K and 512Kbytes caches                        | 75 |

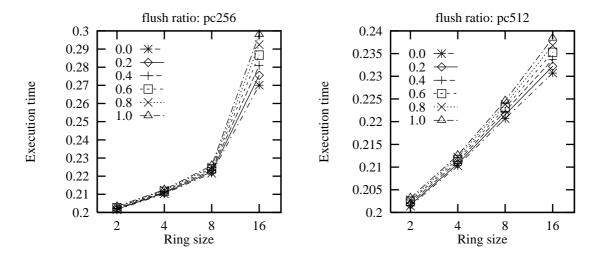

| 5. | 4  | Effect of conflict misses on the performance of paths() with 256K and 512Kbytes caches                        | 75 |

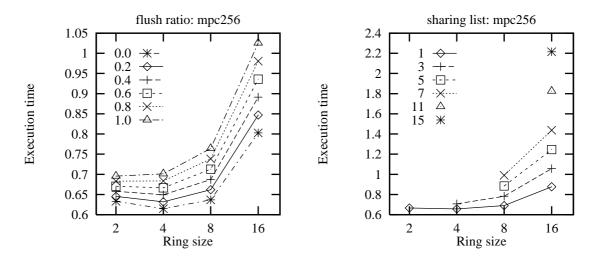

| 5. | 5  | Effects on performance of conflict misses and sharing-list length for mp3d() on 256Kbytes coherent caches     | 77 |

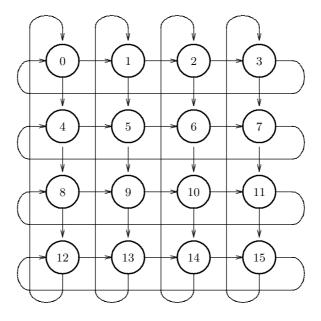

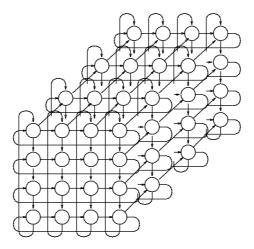

| 6. | 1  | A four-by-four SCI mesh                                                                                       | 79 |

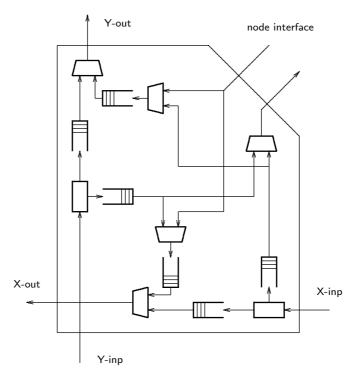

| 6. | 2  | Data paths of a two-dimensional SCI switch                                                                    | 80 |

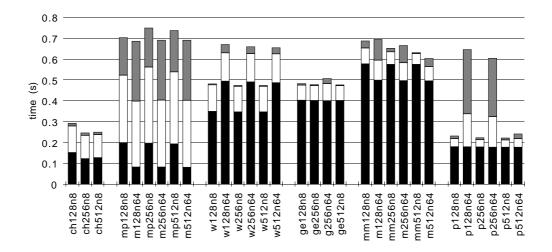

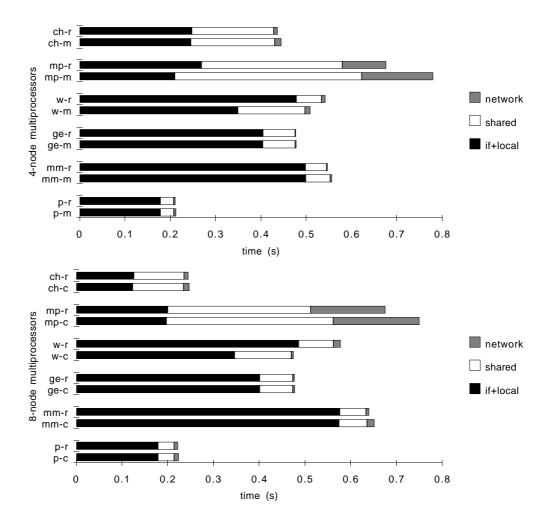

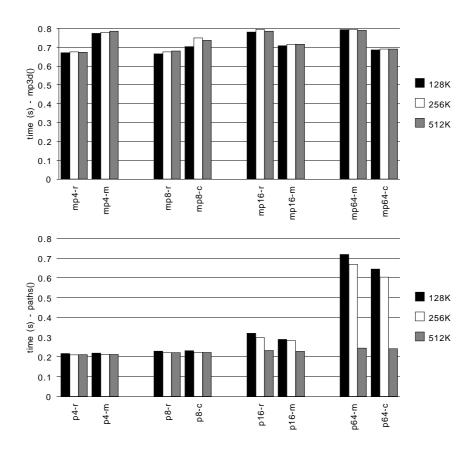

| 6. | 3  | Execution time plots for chol(), mp3d() and water()                                                           | 82 |

| 6. | 4  | Coherent cache shared-data read hit ratio plots for chol(), mp3d() and water()                                | 82 |

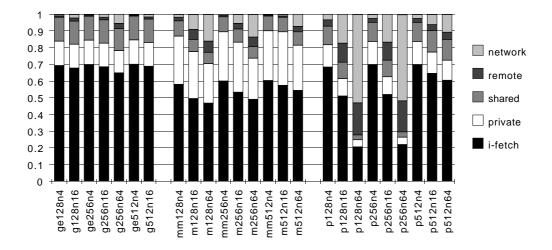

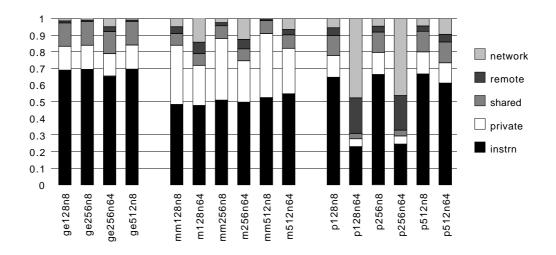

| 6. | 5  | Execution time breakdown for chol(), mp3d() and water()                                                       | 83 |

| 6. | 6  | Execution time plots for ge(), mmult() and paths()                                                            | 84 |

| 6. | 7  | Coherent cache shared-data read hit ratio plots for ge(), mmult() and paths()                                 | 85 |

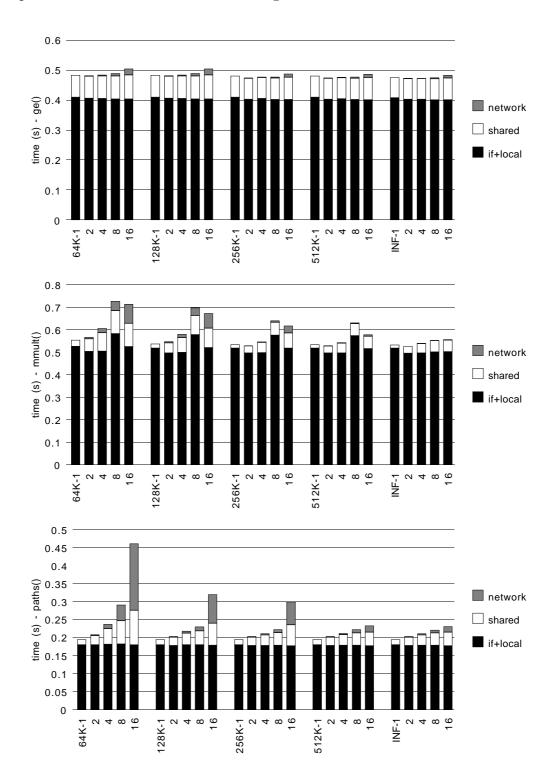

| 6. | 8  | Execution time breakdown for ge(), mmult() and paths()                                                        | 85 |

| List of Figures | viii |

|-----------------|------|

| List of Figures | V111 |

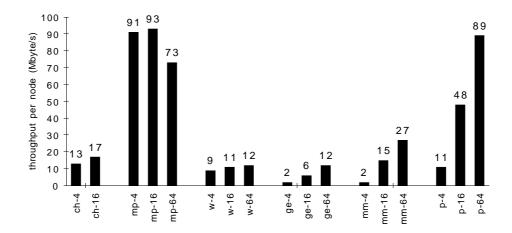

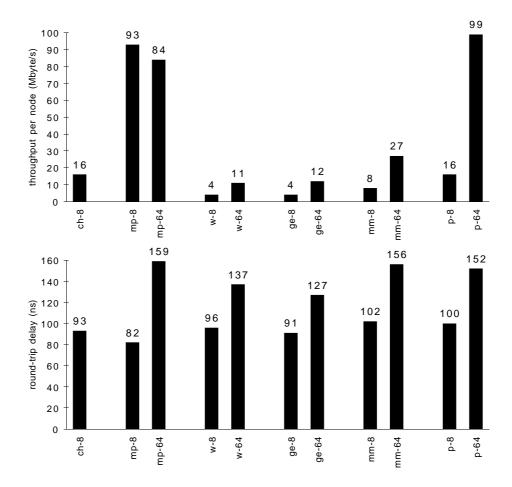

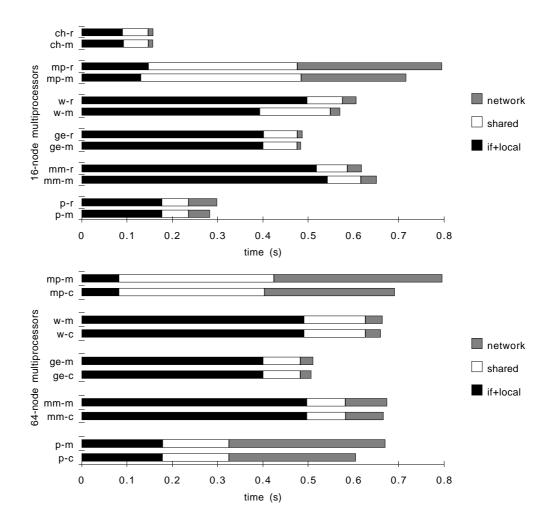

| 6.9  | Throughput per node for 256Kbytes caches                                                                                      | 86  |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.10 | Round-trip delays for 256Kbytes caches                                                                                        | 86  |

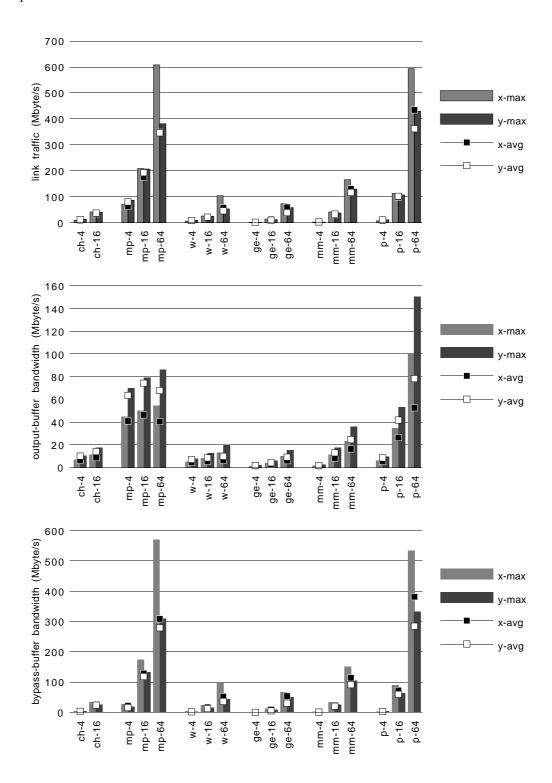

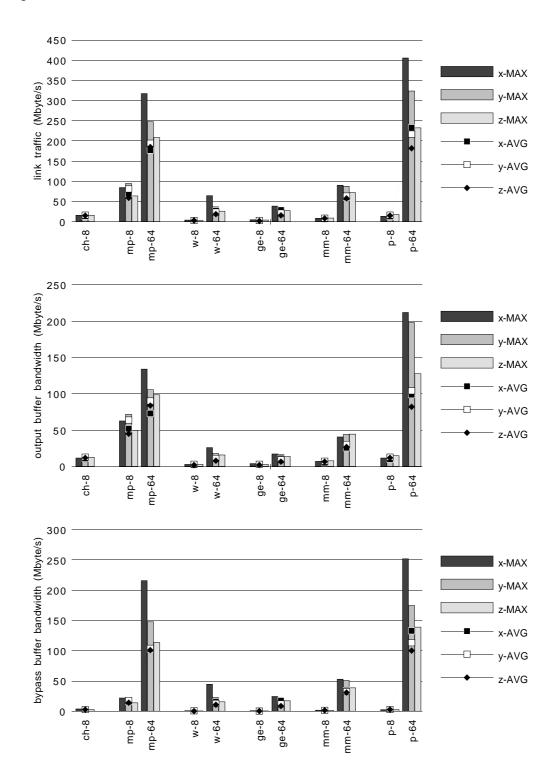

| 6.11 | Link traffic per dimension, output buffer traffic per dimension and bypass buffer traffic per dimension, for 256Kbytes caches | 88  |

| 6.12 | A four-by-four SCI cube                                                                                                       | 89  |

| 6.13 | Execution time plots for chol(), mp3d(), water(), ge(), mmult() and paths()                                                   | 90  |

| 6.14 | Coherent cache shared-data read hit ratio plots for chol(), mp3d(), water(), ge(), mmult() and paths()                        | 90  |

| 6.15 | Execution time breakdown for chol(), mp3d() and water()                                                                       | 91  |

| 6.16 | Execution time breakdown for ge(), mmult() and paths()                                                                        | 92  |

| 6.17 | Throughput per node and round-trip delay, for 256Kbytes caches                                                                | 93  |

| 6.18 | Link traffic per dimension, output buffer traffic and bypass buffer traffic, all for 256Kbytes caches                         | 94  |

| 6.19 | Performance of 4-node and 8-node multiprocessors, with 256Kbytes caches                                                       | 95  |