# 1 Interrupções no MIPS

O 'processador' do MIPS executa as "instruções de usuário" dos programas, que são as instruções que estudamos até agora.

O Control Processor  $\theta$  (CP0) é o 'co-processador' que executa as instruções que controlam o ambiente em que os programas de usuário executam. Estas "instruções de controle" são usadas para implementar sistemas operacionais, através de trocas — bem-comportadas — de execução em modo usuário para execução modo sistema, além do tratamento de todas as condições excepcionais que possam ocorrer durante a execução de um programa. Por ora, nos interessam as interrupções.

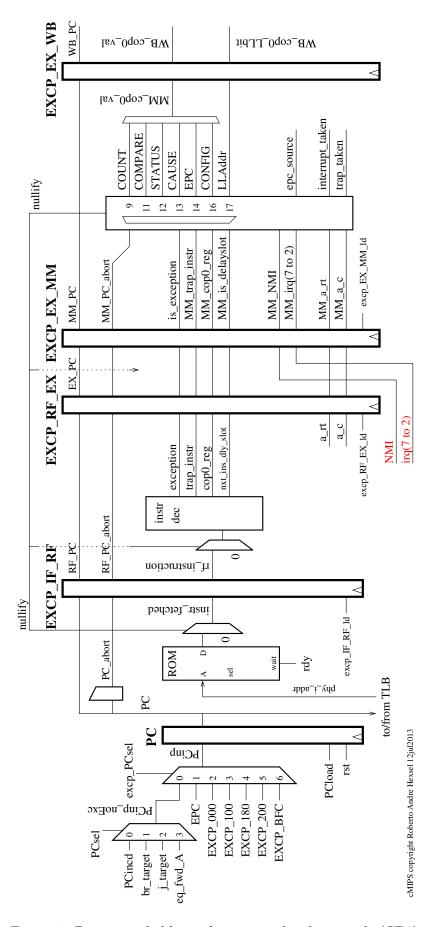

Os sinais de interrupção, gerados pelos dispositivos de Entrada e Saída (ES), são amostrados pelo registrador de segmento EXCP\_EX\_MM, que "une e separa" os segmentos de execução e memória, como mostra a Figura 1.

Quando uma interrupção é detectada, o CP0 verifica se o evento sinalizado pode ser atendido — quem decide pela viabilidade do atendimento é o projetista do SO. Se o evento pode ser tratado, o estado de execução do processador é alterado para "modo sistema", o endereço da instrução que seria executada, não fosse a ocorrência da interrupção, é salvado, e a execução desvia para o código que trata as interrupções.

A instrução que seria executada, é chamada de "causadora", e seu endereço é salvado no registrador  $\mathsf{EPC}$  ( $\mathit{Exception}\ PC$ ).

Figura 1: Diagrama de blocos do processador de controle (CP0).

### 1.1 Registradores do Control Processor 0 – CP0

Os títulos das próximas seções indicam o número do registrador no CP0, e a página de sua definição completa, em

MIPS32 Architecture for Programmers, Volume III: The MIPS32 Privileged Resource Architecture, MIPS Technologies, Rev. 2.50, 2005.

### 1.1.1 Status (CP0-12, pg.79)

O registrador **Status** define o modo de execução do processador, e quais são as interrupções habilitadas.

Este registrador é atualizado por hardware e alguns bits podem ser alterados por software.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12      | 11  | 10    | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02  | 01  | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|-----|-------|----|----|----|----|----|----|----|-----|-----|----|

|    |    |    |    |    |    |    | 2  | X  |    |    |    |    |    |    |    |    |    | IN | $I_7$ . | .IN | $I_0$ |    |    |    | 0  |    | UM | 0  | ERL | EXL | IE |

|    |    |    |    |    |    |    |    |    | -  |    |    |    | -  |    |    |    |    |    |         |     |       | ٠. |    |    |    |    |    |    |     |     |    |

$\mathsf{IM}_7..\mathsf{IM}_0$  interrupt mask; se bit  $\mathsf{IM}_i{=}1$  então a interrupção de nível i está habilitada;

UM user mode, UM=1 indica modo usuário, UM=0 indica modo sistema;

ERL at error level, ERL=1 quando ocorre um dentre Reset, SoftReset, NMI ou CacheError;

EXL at exception level, EXL=1 quando ocorre uma exceção que não seja Reset, SoftReset, NMI ou CacheError;

IE interrupt enable, IE=1 indica que as interrupções estão habilitadas.

Os campos IM, UM, IE podem ser alterados por software.

# 1.1.2 Cause (CP0-13, pg.92)

O registrador Cause indica a causa da excessão mais recente.

Este registrador é atualizado por hardware e alguns bits podem ser alterados por software.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | $^{24}$ | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12      | 11  | 10 | 09 | 08 | 07 | 06 | 05 | 04  | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|---------|-----|----|----|----|----|----|----|-----|----|----|----|----|

| BD | ΤI | 0  | 0  | DC | 0  | 0  | 0       | IV |    |    |    | Х  |    |    |    |    |    | I  | $P_7$ . | .IP | 0  |    |    | 0  |    | Ex | сСс | de |    | (  | )  |

BD in branch delay, BD=1 indica que a última exceção ocorreu num delay slot;

Tl timer interrupt, TI=1 indica que há uma interrupção do temporizador pendente;

DC disable Count register, DC=1 desabilita o contador interno; DC=0 habilita o contador. Usado para reduzir dissipação de energia em aplicações de baixo consumo;

IV interrupt uses general exception vector, IV=0 para tratamento de interrupções como se fossem exceções (0x180); IV=1 para o tratamento das interrupções ser desviado para o vetor de interrupções (0x200). Este (IV=1) é o modo usado no software do cMIPS;

$IP_7...IP_0$  interrupção pendente; se bit  $IP_i=1$  então a interrupção de nível j está pendente;

ExcCode exception code, identifica a exceção, veja os códigos na Tabela 1.

Os campos TI, DC podem ser alterados por software.

|         |     | _                    | ,                                          |

|---------|-----|----------------------|--------------------------------------------|

| binário | dec | mnem                 | causa da excessão                          |

| 00000   | 0   | Int                  | interrupção                                |

| 00001   | 1   | $\operatorname{Mod}$ | modificação de página (modificação na TLB) |

| 00010   | 2   | TLBL                 | excessão da TLB (load ou busca)            |

| 00011   | 3   | TLBS                 | excessão da TLB (store)                    |

| 00100   | 4   | AdEL                 | erro de endereçamento ( $load$ ou busca)   |

| 00101   | 5   | AdES                 | erro de endereçamento $(store)$            |

| 00110   | 6   | $_{\mathrm{IBE}}$    | erro no barramento de instruções           |

| 00111   | 7   | DBE                  | erro no barramento de dados                |

| 01000   | 8   | Sys                  | syscall                                    |

| 01001   | 9   | Bp                   | break point                                |

| 01010   | 10  | RI                   | instrução reservada (opcode inválido)      |

| 01100   | 12  | Ov                   | over flow                                  |

| 01101   | 13  | $\operatorname{Tr}$  | trap                                       |

| 11111   | 31  | _                    | nenhuma excessão pendente                  |

Tabela 1: Códigos de excessão, bits 6 a 2 do registrador Cause.

## 1.1.3 EPC (CP0-14, pg.97)

Contém o endereço no qual o processamento reinicia após o tratamento de uma interrupção ou excessão. O conteúdo do EPC é atualizado pelo processador na ocorrência de uma excessão (ou interrupção) se Status.EXL=0.

O conteúdo de EPC pode ser alterado e/ou consultado por software.

#### 1.2 Instruções de controle

São duas as instruções usadas para acessar os registradores do CP0: mfc0 (move from coprocessor  $\theta$ ), e mtc0 (move to coprocessor  $\theta$ ). As duas tem dois argumentos, um dos 32 registradores de uso geral, e o número de um registrador do CP0.

```

mfc0 r5, c0_status  # r5 <- Status

mtc0 r6, c0_cause  # Cause <- r6</pre>

```

A instrução eret (exception return) copia o conteúdo do EPC para o PC, e faz STATUS\_EXL←0.

#### 1.3 Mascaramento de interrupções

São oito as interrupções disponíveis no cMIPS. As interrupções de nível 7 a 2 são as cinco interrupções por *hardware* e que podem ser ligadas a dispositivos externos.

As interrupções são apelidadas de irq, de *Interrupt ReQuest*. A irq7 é associada ao contador interno, a irq6 é ligada à UART, e a irq5 é ligada ao contador externo. As interrupções irq1 e irq0 são interrupções "por *software*" e podem ser disparadas por escritas no registrador Cause.

O programador pode habilitar individualmente cada interrupção ao escrever em Status.IM, ligando ou desligando as "máscaras de interrupção". O trecho de código abaixo habilita as interrupções irq7 e irq6 e desabilita todas as demais.

Ao tratar uma interrupção, para determinar quais são as interrupções pendentes, e que  $n\tilde{a}o$   $est\tilde{a}o$  mascaradas, basta fazer um and de Status.IM com Cause.IP.

```

tratador:

mfc0 k0, c0_cause  # k0 <- Cause.IP

mfc0 k1, c0_status  # k1 <- Status.IM

andi k1, k1, 0xff00  # mantém somente bits IM

and k1, k0, k1  # k1 <- IP AND IM

... # trata interrupções da maior para a menor prioridade

```

# 1.4 Alterações no estado do processador

Suponha que uma interrupção é detectada após a decodificação da instrução no endereço 1023 e durante a busca da instrução no endereço 1024. As seguintes alterações no CP0 ocorrem automaticamente e no mesmo ciclo:

```

\begin{array}{lll} \mathsf{EPC} \leftarrow 1024 & \mathsf{salva} \ \mathsf{endereço} \ \mathsf{da} \ \text{``causadora''} \\ \mathsf{Status}.\mathsf{EXL} \leftarrow 1 & \mathsf{entra} \ \mathsf{em} \ \mathit{EXception} \ \mathit{Level} \\ \mathsf{Cause}.\mathsf{ExcCode} \leftarrow 0 & \mathsf{sinaliza} \ \mathsf{interrup\~{c}ao} \ \mathsf{(cfe. Tabela 1)} \\ \mathsf{Cause}.\mathsf{IP} \leftarrow \mathsf{irq}_i \ \mathsf{irq}_j \ \ldots & \mathsf{mostra} \ \mathsf{interrup\~{c}ae} \ \mathsf{pendentes} \\ & \mathit{anula} \ \mathit{instru\~{c}ae} \ \mathsf{em} \ \mathsf{BUSCA}, \ \mathsf{DECOD}, \ \mathsf{EXEC} \\ \mathsf{PC} \leftarrow \& ( \ \mathsf{tratador}() \ ) & \mathsf{salta} \ \mathsf{para} \ \mathsf{tratador} \\ \end{array}

```

As interrupções somente são aceitas se Status.EXL = 0 e Status.ERL = 0 e Status.IE = 1. Ao aceitar uma interrupção, o CP0 faz Status.EXL = 1, o que automaticamente desabilita outras interrupções. Além disso, o software decide pelo tratamento em função do mascaramento.

# 1.5 Código do tratador

Programa 1: Esqueleto/protótipo de um tratador de interrupção.

```

1

void tratador(void) {

2

volatile regCause Cause; // record descreve reg Cause

3

Cause = le_reg_cause();

4

// habilita interrupcoes(); // SE permite aninhamento

5

6

// descobre causa da interrupção e trata evento

7

switch (Cause.IP) {

case IRQ7: // Count == Compare

9

// trata do evento mais prioritário

10

case IRQ6: // UART

11

12

// trata da segunda prioridade

13

default:

// contador externo

// trata dos outros eventos

14

}

15

// desabilita_interrupcoes(); // SE permite aninhamento

16

retorna_para_causadora();

17

18

```

Qual deve ser o ambiente de execução para suportar tratadores escritos em C?

Código completo está em cMIPS/include/{start.s,handlers.s}.

Programa 2: Tratador/despachante de interrupções – versão cMIPS.

```

# interrupções separadas das excessões

excp 0200:

2

mfc0 k1, c0_status

mfc0 k0, c0_cause

3

andi k1, k1, 0xff00 # keep only IP bits from Status

4

k0, k0, k1

# and mask them off with IM bits

and

5

# keep 3 MS bits of IP (irq7..5)

k0, k0, 10

6

srl

k1, %hi(handlers_tbl) # + 8 By displ in j-table

7

lui

k1, k1, %lo(handlers_tbl)

k1, k1, k0

# add displacement to base of j-table

9

and jump (indirectly) to handler

10

jr

k1

11

nop

12

handlers_tbl:

13

j dismiss

# no request: 000

14

15

nop

16

17

j extCounter

# lowest priority, IRQ5: 001

18

nop

19

# mid priority, IRQ6: 010 = 01x

j UARTinterr

20

nop

21

# mid priority, IRQ6: 011

j UARTinterr

22

23

nop

24

# highest priority, IRQ7: 100 = 1xx

j countCompare

25

26

nop

# highest priority, IRQ7: 101

27

j countCompare

28

nop

j countCompare

# highest priority, IRQ7: 110

29

nop

30

# highest priority, IRQ7: 111

31

j countCompare

32

nop

33

dismiss: # No pending request, must have been noise, just return

34

35

# Return from interrupt

36

eret

```

Programa 3: Tratador de interrupções simples, contador da Seção 7.1.

```

# do not use r1=at

1

.set noat

extCounter:

# Handles IP5 = external counter

k0, HW_counter_addr

3

lа

r0, 0(k0)

# Reset counter, remove IRQ

4

SW

k1, 0xc0000100

# Count 256 clock pulses & interr

li

5

k1, 0(k0)

# Reload counter so it starts again

6

sw

k0, count_acum

7

la

k1, 0(k0)

# Increment time accumulator

lw

8

9

addi k1, k1, 1

10

sw

k1, 0(k0)

eret

# Return from interrupt

11

```