UFPR – Bacharelado em Ciência da Computação Cl212 – Organização e Arquitetura de Computadores Segunda Lista de Exercícios

[v1.3, 18ago08]

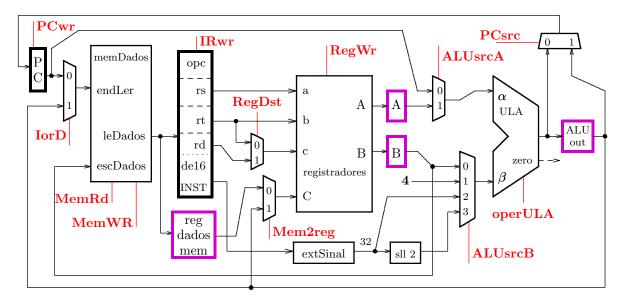

1) Mostre as ligações adicionais necessárias para a implementação das instruções PUSH e POP no processador multiciclo do Capítulo 5, cujo diagrama de blocos está em anexo. Adicione quaisquer recursos que julgar necessários. Mostre os ramos da máquina de estados que implementam estas instruções e indique claramente quais sinais são ativos em cada estado.

```

push r1 # sp := (sp - 4); Mem[ sp ] := r1

pop r1 # r1 := Mem[ sp ]; sp := (sp + 4)

```

2) Considere um novo mode de endereçamento a ser adicionado ao conjunto de instruções do MIPS. Neste modo, o primeiro operando e o resultado são o mesmo registrador e o segundo operando é buscado em memória. Por exemplo, a instrução addm é definida como

```

addm r1, desloc(r2) # r1 := r1 + Mem[ desloc + r2 ]

```

- (a) Mostre como implementar a instrução addm no processador com relógio ciclo longo do Capítulo 5. Adicione quaisquer circuitos necessários e indique os sinais que controlam a execução desta instrução; (b) desenhe um diagrama de tempo para a execução desta instrução no processador com suas adições; (c) mostre como implementar a instrução addm no processador com relógio multiciclo do Capítulo 5. Adicione quaisquer circuitos necessários e mostre o ramo da máquina de estados que controla a execução desta instrução; (d) desenhe um diagrama de tempo para a execução desta instrução no processador do item (c).

- 3) Nas respostas de provas desta disciplina ocorrem com alguma freqüência instruções como lws, com uma semântica que imagino ser a mostrada no comentário.

```

lws r1, r2 ,r3  # r1 := Mem[ r2 + r3 ]

Mostre uma possível implementação desta instrução no processador multiciclo do diagrama.

```

- 4) A instrução JAL (jump and link) permite desviar para uma função, lembrando do endereço de retorno. A instrução JR (jump register) permite carregar o endereço de retorno da função no PC, assim efetuando o retorno de função. (a) Mostre no diagrama acima como implementar estas instruções, acrescente todas as ligações e componentes que julgar necessário; (b) desenhe os ramos da máquina de estados correspondentes a estas instruções e indique os eventos relevantes em cada estado.

- 5) A instrução JM (jump-memory) é similar a uma instrução LW, mas o valor copiado da memória é gravado no PC e não no registrador rt. (a) Mostre no diagrama como implementar esta instrução, acrescente todas as ligações e componentes que julgar necessário; (b) desenhe o ramo da máquina de estados correspondente a esta instrução e indique os eventos relevantes em cada estado; (c) mostre uma possível codificação da instrução JM.

- 6) A instrução LDI (load-indirect) é similar a uma instrução LW, mas o endereço efetivo da palavra a ser copiada para o registrador destino é obtido da posição de memória apontada por [rs + ext(des1)]. (a) Mostre no diagrama como implementar esta instrução, acrescente todas as ligações e componentes que julgar necessário; (b) desenhe o ramo da máquina de estados correspondente a esta instrução e indique os eventos relevantes em cada estado.

- 7) Considere o processador multiciclo descrito no Capítulo 5 do livro texto. Algumas das unidades funcionais completam suas tarefas em 50ps, 100ps e 200ps. O projeto no livro pressupõe um relógio de 200ps, que é o pior caso. Um projeto alternativo consiste em usar relógio de 100ps, no qual as unidades funcionais mais lentas usam dois ciclos de 100ps para completar suas tarefas, já que elas necessitam de 200ps para tal. Por exemplo, no projeto do livro, uma instrução LW consome 5 ciclos de 200ps; no projeto alternativo, ela consumiria 8 ciclos de 100ps: 2 na busca, 1 na decodificação, 2 na execução, 2 no acesso à memória e 1 para gravar resultado. (a) Para os dados abaixo, qual a arquitetura com menor CPI? (b) Qual a mais rápida?

Freqüência de execução de instruções: lw 25%, sw 15%, beq 20%, alu 30%, j 2%

- 8) Considere o processador multiciclo do Capítulo 5. Um programa tem a seguinte mistura de instruções: alu 40%, lw 25%, sw 15%, beq 20%. Considere as três implementações do processador listadas e responda: (a) qual das três é a mais rápida? (b) existem outras misturas de instruções que fariam outra máquina mais rápida, se sim, qual (ou quais)?

- (i) o processador visto em aula (diagrama), com clock de 1GHz (1ns);

- (ii) um processador similar ao do item (i), exceto que a atualização dos registradores ocorre no mesmo tic de relógio em que uma leitura de memória, ou uma operação de ULA completam. Esta versão tem clock de 800MHz (1,25ns) porque a atualização dos registradores alonga o ciclo do relógio.

- (iii) um processador similar ao do item (ii), exceto que o cálculo do endereço efetivo ocorre no mesmo ciclo em que o acesso à memória. Esta versão possui clock de 500MHz (2ns) por causa do longo intervalo necessário para o cálculo do endereço e o acesso à memória.