## CI212 - Organização e Arquitetura de Computadores Primeira Prova

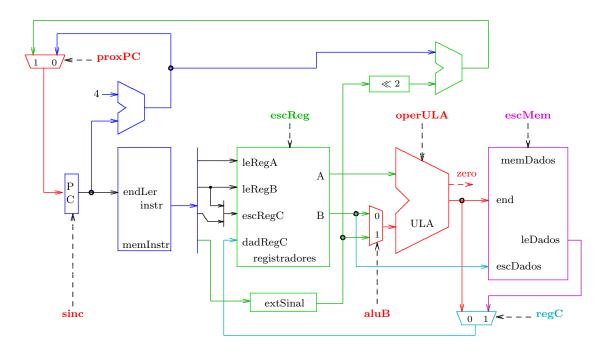

- 1) Enuncie TODAS as técnicas para eliminar (a) dependências de dados, e (b) dependências de controle. Indique *claramente* qual tipo/s de bolha/s é/são eliminada/s por qual das técnicas listadas nos ítens (a) e (b). Um diagrama do processador segmentado do Capítulo 6 pode auxiliar. [6 pontos]

- 2) Considere um novo modo de endereçamento a ser adicionado ao conjunto de instruções do MIPS. Neste modo, o primeiro operando e o resultado são o mesmo registrador e o segundo operando é buscado em memória. A instrução addm é definida como

addm r1, desl(r2) # r1 = r1 + Mem[ desl + r2 ].

- (a) Mostre como implementar a instrução addm no PROCESSADOR COM CICLO LONGO do Capítulo 5 (diagrama abaixo). Adicione quaisquer circuitos necessários [6 pontos].

- (b) Desenhe um diagrama de tempo com a execução desta instrução no processador com suas adições [6 pontos].

- (c) Explique porque seria difícil acrescentar esta instrução ao processador segmentado do Capítulo 6 [4 pontos].

3) Considere um circuito combinacional que não é segmentado e têm latência T. A taxa de computação é 1/T para este circuito. O ganho de desempenho de uma implementação segmentada pode ser modelado pela Equação 1, na qual T é a latência do circuito original sem segmentação, S é o atraso adicional introduzido pelos registradores e k é o número de estágios, supondo que a computação possa ser dividida em k estágios iguais.

$$G = \frac{1}{(T/k+S)}$$

(1) Assim,  $(T/k+S)$  é o tempo mínimo necessário para a computação em cada estágio do novo sistema, e  $1/(T/k+S)$  é sua taxa de computação (throughput).

A Equação 1 é similar à Lei de Amdahl. (a) Descreva a relação entre estas duas equações, e (b) dê uma explicação intuitiva para a semelhança entre as duas equações. [8 pontos]

## Segunda Prova

- 1) Considerando a organização interna de um circuito integrado de memória dinâmica (DRAM), (a) indique uma maneira de aumentar a vazão na sua interface de dados, otimizando para uso num sistema com memória cache; e (b) indique uma maneira de aumentar a vazão no barramento de dados, também considerando o uso em sistema com memória cache. [10 pontos]

- 2) (a) Escreva a equação do tempo de acesso para leitura de um setor num disco e explique sucintamente a contribuição de cada termo para o desempenho global do sistema de E/S. (b) Desenhe um diagrama CLARO E LIMPO que mostre a(s) diferença(s) entre RAID-4 e RAID-5. Explique a(s) diferença(s). [5 pontos].

- 3) Considere um computador que usa entrada e saída por programa para transferir dados da memória para um periférico, empregando o programa abaixo. Calcule a taxa máxima de transferência possível com este código para transferências de 4096 bytes, alinhados com as linhas de cache. O tempo de acesso à memória é de 10 ciclos numa falta e 2 ciclos num acerto. Um acesso ao barramento de E/S custa 25 ciclos. A cache têm linhas com 16 palavras. Ignore faltas na cache de instruções e bolhas causadas por dependências de dados ou de controle. O relógio do processador é de 1GHz (1ns), e o barramento têm largura de uma palavra. [5 pontos]

```

la $10, 0x10000000  # endereço do buffer

la $20, 0xFFFF0000  # endereço do periférico

movi $2, 1024  # tamanho do bloco (pals)

loop: lw $1, 0($10)

addi $10, $10, 4  # apontador para fonte

addi $2, $2, -1  # contador do loop

sw $1, 0($20)  # endereço do periférico

bne $2, $0, loop

```

4) Mantendo os dados da pergunta anterior, considere transferências por acesso direto à memória (DMA). Transferências por DMA desviam da cache, assim como os acessos ao barramento de E/S. O atendimento à interrupções custa 80 ciclos. O código de inicialização do controlador de DMA é mostrado abaixo. (a) Qual a taxa máxima de transferência possível para blocos de 4096 bytes? (b) Qual o tamanho de transferência que tornaria DMA menos/mais atrativo que o laço da questão anterior? [10 pontos]

```

la $10, 0x10000000 # endereço do buffer

la $20, 0xFFFF0000 # endereço do periférico

movi $2, 1024 # tamanho do bloco (pals)

la $9, 0xFFFF0080 # ender controlador de DMA

sw $10, FONTE($9)

sw $20, DEST($9)

sw $2, TAM($9) # dispara a transferência

# DMA efetua transferência e interrompe ao completar

```

## **Prova Final**

1) Mostre o código MIPS necessário para implementar os comandos em C abaixo:

```

int a, b, i, j, x[NNN], y[MMM], z[PPP];

a = 16 * y[65000];

b = x[ y[ z[j] ] ];

[20 pontos]

```

2) Considere a execução do trecho de código ao lado no processador segmentado de 5 estágios. (a) Modifique o código para que ele execute corretamente num processador SEM lógica de bloqueios (stalls) e nem de adiantamento. (b) Re-escreva o código para que ele execute com um mínimo de bolhas, ainda no processador sem adiantamento e nem bloqueios. (c) Qual o número de ciclos para a execução do trecho de código um processador COM adiantamento e COM bloqueios? (d) Qual o ganho de desempenho da resposta de (b) com relação à resposta de (c)? [40 pontos]

```

;; mult executa como add

;; r8 escalar, r9 limite

loop: lw r0, 0(r4)

lw r2, 0(r6)

mult r4, r2, r0

add r4, r4, r8

st r4, 0(r8)

addi r4, r4, 8

addi r6, r6, 8

addi r8, r8, 8

bne r8, r9, loop

```

3) (a) Projete e desenhe um diagrama DETALHADO de uma cache de mapeamento de endereços (TLB) com 32 blocos e associatividade quaternária. Cada bloco contém um mapeamento, o processador emite endereços de 32 bits, o endereço físico possui 34 bits, e as páginas virtuais tem 4Kbytes. (b) Indique como um endereço virtual é interpretado pelo controlador da TLB. (c) Qual o tamanho da Tabela de Páginas em memória? (d) Mostre como organizar a Tabela de Páginas em dois níveis. [40 pontos]