### Revisão - segmentação

- Todos os processadores modernos usam segmentação

- segmentação não reduz a latência de uma instrução mas ajuda na vazão/produção do programa inteiro → várias tarefas em execução simultânea usando recursos distintos

- ganho potencial:  $\approx$  número de estágios CPI: 3-5  $\rightarrow$  1

- vazão do pipeline limitada pelo estágio mais lento estágios desbalanceados reduzem ganho tempo para encher e para drenar segmentos reduz ganho

- controle deve detectar e resolver riscos bloqueios afetam vazão negativamente

- esta aula: controle dos segmentos (e de riscos)

UFPR BCC CI212 2016-2— controle dos sgmtos

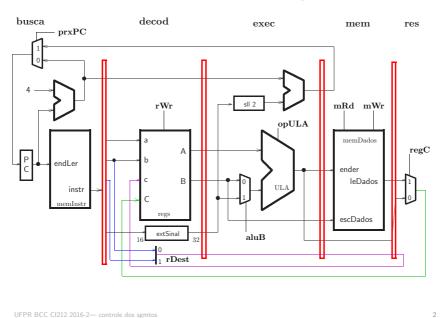

### Controle em Processador Segmentado

|     | exec  |       |      |       | mem | res |     |      |

|-----|-------|-------|------|-------|-----|-----|-----|------|

|     | rDest | opULA | aluB | prxPC | mRd | mWr | rWr | regC |

| ALU | 1     | fun   | 0    | 0     | 0   | 0   | 1   | 0    |

| IMM | 0     | oper  | 1    | 0     | 0   | 0   | 1   | 0    |

| lw  | 0     | +     | 1    | 0     | 1   | 0   | 1   | 1    |

| SW  | х     | +     | 1    | 0     | 0   | 1   | 0   | х    |

| beq | х     | _     | 0    | 1     | 0   | 0   | 0   | х    |

registradores dos segmentos são atualizados a cada ciclo **busca** e **decod**: sempre busca instrução e incrementa PC

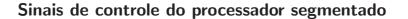

### **Controle em Processador Segmentado**

Todos os sinais de controle são determinados na decodificação e mantidos nos registradores entre os estágios

UFPR BCC Cl212 2016-2— controle dos sgmtos

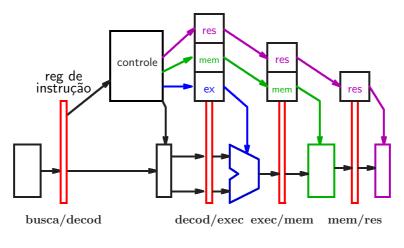

## **Controle do Processador Segmentado**

UFPR BCC CI212 2016-2- controle dos sgmtos

### Modelo seqüencial de execução

5

6

Conjunto de instruções de processadores "comuns" define um **modelo seqüencial de execução:**

cada instrução é completamente executada e altera o estado do processador antes do início da próxima instrução

Este modelo facilita muito a vida do programador!

Como programador em C pensa que cada comando executa? if(p == q) { x = y + z; t = w \* z; }; a = b - c;

#### **Riscos em processadores segmentados**

Riscos são condições que levam a comportamento incorreto se as medidas apropriadas não forem tomadas

• riscos estruturais structural hazards > quando duas instruções diferentes necessitam do mesmo recurso no mesmo ciclo riscos com dados data hazards > quando 2 instr diferentes usam mesmo local de armazenamento ▷ resolução do risco deve garantir aparência de que instruções executaram na ordem seqüencial correta • riscos de controle control hazards > quando uma instrução determina quais instruções serão executadas a seguir (desvios, saltos, funções)

UFPR BCC CI212 2016-2- controle dos semtos

### **Riscos com dados**

7

8

9

Quando duas instruções diferentes usam data hazards mesmo local de armazenamento

Deve parecer que instruções executam na ordem següencial correta

i:  $r1 \leftarrow r4 + r5$ j:  $r2 \leftarrow r1 - r9$  r1 foi produzido por i k: r1  $\leftarrow$  r6  $\oplus$  r3 valor de r1 em i é sobre-escrito resultado de i;j;k é o mesmo que i;k;j ?

Convenção: nome do risco é a ordem do programa que deve ser preservada pela implementação (segmentada, superescalar)

UFPR BCC CI212 2016-2- controle dos semtos

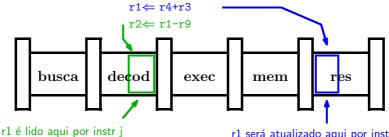

Riscos com dados - RAW

Read-After-Write (RAW)

instr i tenta ler operando r1 ANTES que instr i escreva resultado

- i:  $r1 \leftarrow r4 + r3$

- j: r2 ⇐ r1 r9

- Risco decorre de uma dependência de dados, causada pela comunicação entre as duas instruções add e sub através de r1

UFPR BCC Cl212 2016-2- controle dos semtos

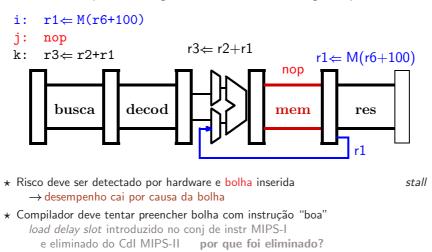

### Solução (parcial) simples para RAW

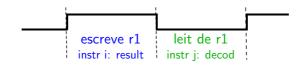

- Circuito de controle detecta risco, e então insere bolha: atrasa instrução j até ocorrer escrita do resultado de i

\* solução simples – segura instrução dependente na busca

- \* desempenho ruim por causa dos ciclos desperdiçados

| i: | r1⇐ r2+r3 | В | D | Ex    | Μ       | $\mathbf{R}$ |    |   |   |

|----|-----------|---|---|-------|---------|--------------|----|---|---|

| j: | r2⇐ r1-r9 |   | В | ullet | $\odot$ | ♦<br>D       | Ex | М | R |

• solução simples pressupõe que, em cada ciclo, registradores são atualizados num semiciclo e são lidos no outro

UFPR BCC CI212 2016-2- controle dos sgmtos

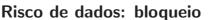

Compara com estágios posteriores

▷ if (rs1(decod)==rd(exec) || rs1(decod)==rd(mem))

{ insere bolha } mesmo para rs2

▷ todos conflitos são riscos? st não escreve reg, addi não lê reg

UFPR BCC CI212 2016-2- controle dos sgmtos

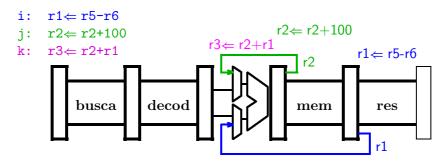

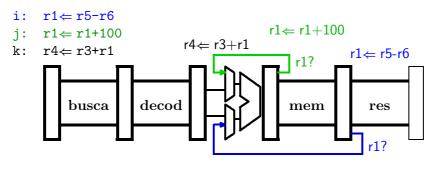

### Risco de dados: adiantamento (i)

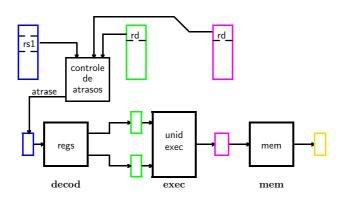

Ao invés de bloquear, adianta resultado para entradas da ULA: usa controle de atrasos para decidir se deve adiantar, e usa multiplexadores para escolher fonte do resultado.

Adiantamento = forwarding, bypassing, short-circuiting

stall

10

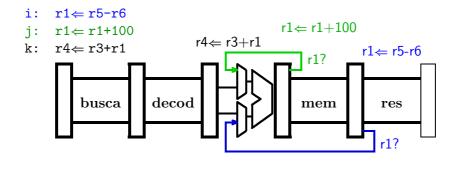

### Risco de dados: adiantamento (ii)

Quem fornece r1 para instrução k?

Implementação deve satisfazer modelo seqüencial de execução senão, os clientes ficarão muito irritados...

UFPR BCC CI212 2016-2- controle dos sgmtos

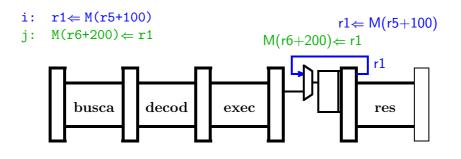

Risco de dados: adiantamento (iii)

Adiantamento para o estágio de memória load seguido de store

UFPR BCC CI212 2016-2- controle dos sgmtos

Adiantamento para o estágio de memória: load seguido por add

13

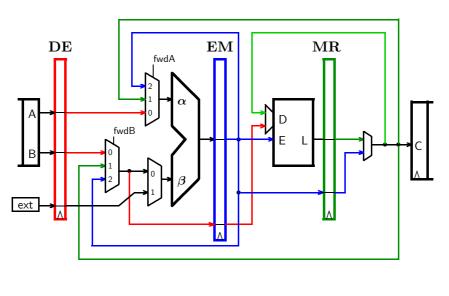

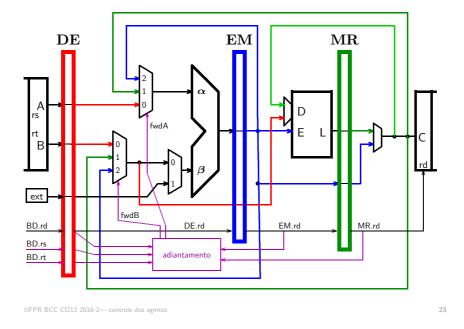

### Adiantamento - implementação

- Adiantamento nas linhas de dependência para trás no tempo

▷ estágio EXEC produz resultado de instr de ULA ou ender efetivo

▷ estágio MEM produz resultado de lw

- Adianta para entradas da ULA valor na saída de qualquer registrador de segmento e não somente do reg. DE:

- \* adiciona multiplexadores nas entradas da ULA

- para passar rd para as entradas rs e rt da ULA

- 0: entrada normal (registrador DE)

- 2: adianta da instrução anterior (registrador EM)

- 1: adianta de duas instruções atrás (registrador MR)

- \* circuito adicional de controle

- permite execução sem bolhas, mesmo com dependências de dados

→ exceto no uso do valor do load...

UFPR BCC CI212 2016-2- controle dos sgmtos

Adiantamento - circuito completo

UFPR BCC Cl212 2016-2- controle dos sgmtos

17

16

## Controle de Adiantamento (1/4)

#### • Risco EX/MEM:

- $\star$  Lembre que o núm do reg de destino (Rd) viaja junto com a instrução

- $\star\,$ rd é registrador destino r<br/>d ou rt

- $\star$ rs é o número do registrador  $\mathbf{rs}$

- $\star$ rt é o número do registrador **rt**

- $\star$  fwdA, fwdB controlam os multiplexadores

- if ( EM.rd == DE.rs ) fwdA = 2 anterior

- if ( EM.rd == DE.rt ) fwdB = 2

• risco MEM/RES:

- if ( MR.rd == DE.rs ) fwdA = 1

if ( EM.rd == DE.rt ) fwdB = 1

- O que está errado no controle?

Quando pode adiantar indevidamente?

Quais seqüências de instruções revelariam o erro?

2 antes

# Controle de Adiantamento (2/4)

| • Risco EX/MEM:                                   |                  |

|---------------------------------------------------|------------------|

| if ( EM.regWR                                     | se instr escreve |

| and ( $EM.rd == DE.rs$ ) )                        | anterior         |

| fwdA = 2                                          |                  |

| O MESMO PARA fwdB                                 |                  |

| • risco MEM/RES:                                  |                  |

| if ( MR.regWR                                     | se instr escreve |

| and ( $MR.rd == DE.rs$ ) )                        | 2 antes          |

| fwdA = 1                                          |                  |

| O MESMO PARA fwdB                                 |                  |

| • O que está errado no controle?                  |                  |

| Quando pode adiantar indevidamente?               |                  |

| Quais seqüências de instruções revelariam o erro? |                  |

|                                                   |                  |

# Controle de Adiantamento (3/4)

| • Risco EX/MEM:                  |                  |

|----------------------------------|------------------|

| if ( EM.regWR                    | se instr escreve |

| and ( $EM.rd$ != 0 )             | dest não é \$r0  |

| and ( $EM.rd == DE.rs$ ) )       | anterior         |

| fwdA = 2                         |                  |

| O MESMO PARA fwdB                |                  |

| • risco MEM/RES:                 |                  |

| if ( MR.regWR                    | se instr escreve |

| and ( $MR.rd != 0$ )             | dest não é \$r0  |

| and ( MR.rd == DE.rs ) )         | 2 antes          |

| fwdA = 1                         |                  |

| O MESMO PARA fwdB                |                  |

| • O que está errado no controle? |                  |

Lembre do modelo seqüencial

UFPR BCC CI212 2016-2- controle dos sgmtos

UFPR BCC Cl212 2016-2— controle dos sgmtos

19

### Controle de Adiantamento (4/4)

UFPR BCC CI212 2016-2— controle dos sgmtos

Adiantamento - circuito completo + controle

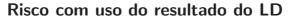

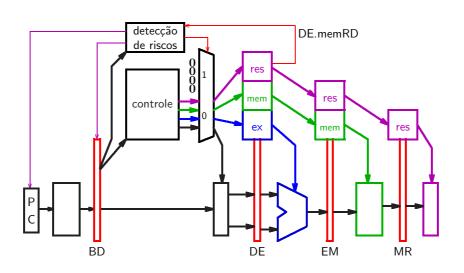

### Risco com uso do resultado do LD

• DECOD deve detectar risco entre LD e usos do seu resultado

```

if ( DE.memRD

and ( ( DE.rt == BD.rs )

or ( DE.rt == BD.rt ) ) )

bloqueia_DE

```

segura segmentos

25

26

- segura segmentos

SE instrução em EXEC lê memória

E LD em EXEC produz operando da instr em DECOD

- depois deste ciclo parado,

lógica de adiantamento resolve os demais riscos

UFPR BCC CI212 2016-2— controle dos sgmtos

### Circuito de controle de bloqueios

Além de detectar os riscos, implementação de bloqueios/stalls deve:

- impedir que instruções em BUSCA e DECOD avançem

→ mantém os conteúdos do PC e do registrador BD

- re-executa a mesma instrução, sem que ela altere estado \* desativar os sinais de controle (muda para 0) nos campos

- de controle dos estágios EXEC, MEM e RES

- $\ast\,$  circuito detector de riscos controla MUX que seleciona entre valores de controle e 0s

- \* pressupõe que 0s são valores inócuos  $\rightarrow$  nada muda esta instrução não altera o estado da computação

- instruções nos demais estágios (EX,MEM,RES) completam normalmente

UFPR BCC CI212 2016-2- controle dos sgmtos

### Circuito de controle de bloqueios

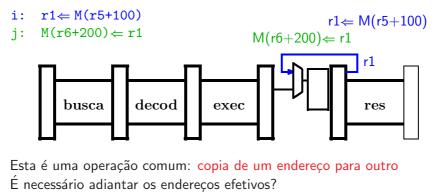

### Risco com LD seguido de ST

Nas cópias memória-memória (LD;ST) pode adiantar saída do registrador MR para a entrada da memória → necessita circuito de adiantamento para estágio de memória

Cuidados especiais com p = \*p; \*p = \*p; \*p = p;

UFPR BCC CI212 2016-2- controle dos sgmtos

## Falta alguma coisa?

addu r5, ... sw r5, ... addu r5, ... subu r6, ... sw r5, ...

Necessita caminho para adiantamento da saída da ULA para entrada de dados da memória.

UFPR BCC CI212 2016-2- controle dos sgmtos

### Resumo (i)

#### Modelo seqüencial de execução

Conjunto de instruções de processadores "comuns" define um **modelo seqüencial de execução:**

cada instrução é completamente executada e altera o estado do processador antes do início da próxima instrução

programador considera que cada comando C executa atomicamente isso não é verdade com segmentação!

bolhas reduzem o paralelismo ~> serializam a computação

28

# Resumo (ii)

- Dependências de dados resolvidas com adiantamento (quase sempre)

- Deve garantir que instruções anteriores escreverão resultado, destino é mesmo que fonte, e instrução anterior não tem prioridade

- Acrescentar circuito de adiantamento onde pode-se adiantar

→ força bloqueio se precisa esperar por resultado

estágio EXEC, MEM para store, DECOD para desvio

- LOADs necessitam parada porque sobrepõem EXEC com MEM desvios podem necessitar de parada também stall=parada

- Próxima aula: riscos de controle e previsão de desvios.

- Exercício: Desenhe, numa folha A3 quadriculada, o circuito completo do processador segmentado, incluindo todos os circuitos mostrados nos slides 5 e 23.

UFPR BCC Cl212 2016-2- controle dos sgmtos