### Processamento Paralelo & Multiprocessadores

2012-2

- Motivação

- Tipos de máquinas paralelas

- Coerência entre caches

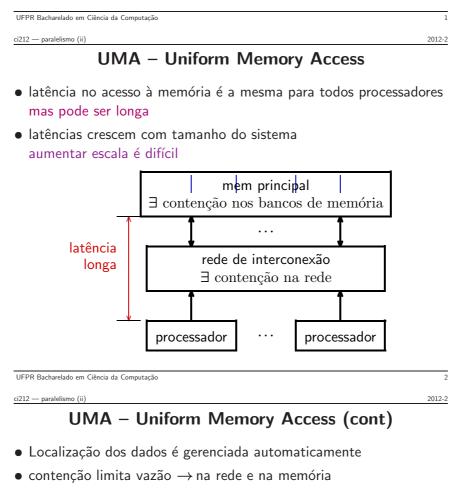

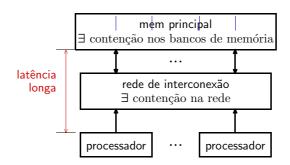

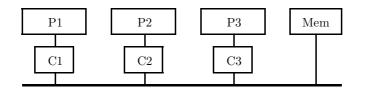

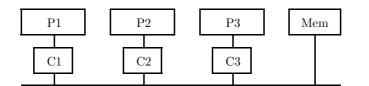

- geralmente usa caches

- usado em pequenos multiprocessadores = MPs simétricos Symmetric MultiProcessors ou SMPs

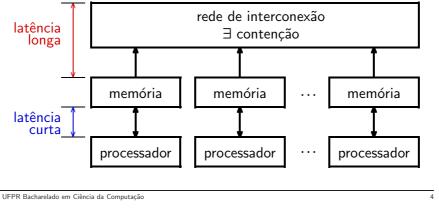

### NUMA – Non-Uniform Memory Access

- Latência pequena no acesso à memória local

- latência grande no acesso à memória remota  $P \rightarrow M_{loc} \rightarrow R \rightarrow M_{rem}$

- vazão para memória local pode ser mais alta que para remota

- $\bullet$  contenção na rede e no acesso à memória  $$\mathsf{P}_{\mathrm{loc}} \times (N\text{-}1)\mathsf{P}_{\mathrm{rem}}$$

ci212 — paralelismo (ii)

## Multiprocessadores NUMA Non-Uniform Memory Access

- Memória logicamente compartilhada mas fisicamente distribuída

um espaço de endereçamento lógico

- ▷ pode ser tratado como memória compartilhada

- desempenho depende fortemente da localização dos dados

- Multicomputadores

ci212 — paralelismo (ii)

- ▷ cada processador tem espaço de endereçamento privativo

- ▷ comunicação através de troca de mensagens (explícita)

UFPR Bacharelado em Ciência da Computação

2012-2

2012-2

2012-2

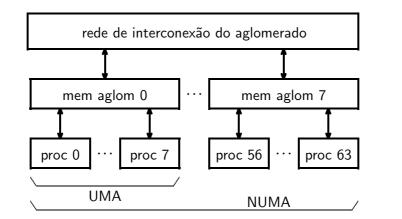

### Aglomerados (clusters)

- Nós UMA pequenos num sistema NUMA grande

- híbrido? aglomerado de aglomerados?

# Processamento Paralelo & Multiprocessadores

- Motivação

- Tipos de máquinas paralelas

- Coerência entre caches

| ci212 — paralelismo | • (ii) |  |

|---------------------|--------|--|

|---------------------|--------|--|

UFPR Bacharelado em Ciência da Computação

### Execução atômica

Dois processadores executam em paralelo:

Quais os valores de "print c" e "print d"?

| a = a + 1; $\equiv$ | lw r1,0(r2)  |

|---------------------|--------------|

|                     | addi r1,r1,1 |

|                     | sw r1,0(r2)  |

| a++; a+=1;          |              |

|                     |              |

UFPR Bacharelado em Ciência da Computação

ci212 — paralelismo (ii)

2012-2

8

2012-2

7

2012-2

| Sincronização e Atomicidade |  |  |

|-----------------------------|--|--|

| elos                        |  |  |

|                             |  |  |

| operações demoradas         |  |  |

| latência + tempo na fila    |  |  |

| emas maiores                |  |  |

|                             |  |  |

|                             |  |  |

Barramento é um meio de comunicação compartilhado

| → comunicação por <b>difusão</b>                                   | broadcast |

|--------------------------------------------------------------------|-----------|

| $\rightsquigarrow$ comunicação é serializada através do barramento |           |

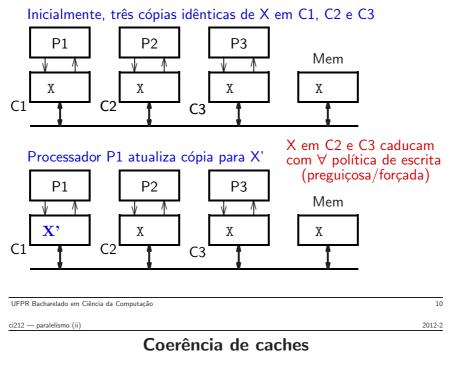

### Coerência de caches

2012-2

P1, P2 e P3 carregam X em suas caches;

P1 atualiza sua versão;

C2 e C3 ficam com sua cópia desatualizada.

$\rightarrow$  isso ocorre **mesmo** que as caches usem

escrita forçada (ou escrita preguiçosa)

Informalmente:

**coerência entre caches** é um método para garantir que os acessos à memória sejam coerentes, apesar das caches.

2012-2

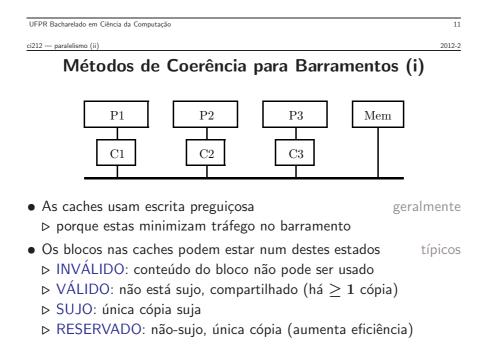

#### Métodos de Coerência para Barramentos (ii)

UFPR Bacharelado em Ciência da Computação

ci212 — paralelismo (ii)

2012-2

#### Métodos de Coerência para Barramentos (iii)

- Espionagem (snooping)

- ▷ todas as caches observam todo o tráfego no barramento

- ▷ etiquetas com duas portas: CPU e barramento

- > ações de um controlador de cache são visíveis pelos demais CCs → difusão no barramento

- O que ocorre nas escritas?

invalidar cópias nas outras caches: protocolos de invalidação

atualizar cópias nas outras caches: protocolos de atualização

UFPR Bacharelado em Ciência da Computação

14 2012-2

#### ci212 — paralelismo (ii)

### Protocolo de Invalidação

| atividade        | atividade              | cache                                 | cache | memória |

|------------------|------------------------|---------------------------------------|-------|---------|

| no processador   | no barramento          | C1                                    | C2    | ender X |

|                  |                        |                                       |       | 0       |

| P1 lê X          | falta em X             | 0                                     |       | 0       |

| P2 lê X          | falta em X             | 0                                     | 0     | 0       |

| P1 faz X=1       | invalidação para X     | 1                                     | _     | 0       |

| P2 lê X          | falta em X *           | 1                                     | 1     | 1       |

| * D1 waamamala à | falta and CO a atualia | · · · · · · · · · · · · · · · · · · · | 1     |         |

\* P1 responde à falta em C2 e atualiza memória

### Protocolo de Atualização

| atividade<br>no processador | atividade<br>no barramento | cache<br>C1 | cache<br>C2 | memória<br>ender X |

|-----------------------------|----------------------------|-------------|-------------|--------------------|

|                             |                            |             |             | 0                  |

| P1 lê X                     | falta em X                 | 0           |             | 0                  |

| P2 lê X                     | falta em X                 | 0           | 0           | 0                  |

| P1 faz X=1                  | broadcast de X=1           | 1           | 1           | 1                  |

| P2 lê X                     | acerto em X                | 1           | 1           | 1                  |

Há mais tráfego no barramento, se P2 não usar X novamente.

UFPR Bacharelado em Ciência da Computação

ci212 — paralelismo (ii)

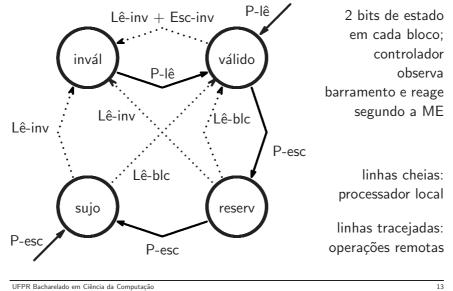

#### Protocolo de Invalidação Simplificado

- Caches usam escrita preguiçosa

- Estados

- ▷ INVÁLIDO: conteúdo do bloco não pode ser usado

- $\triangleright$  COMPART-ilhado: não está sujo, compartilhado (há  $\geq$  1 cópia)

- ▷ EXCLUSIVO: única cópia suja

- a cada transação no barramento, o controlador de cache:

▷ verifica se bloco está na cache

- ▷ se estiver na cache, efetua mudança de estado cfe ME (adiante)

UFPR Bacharelado em Ciência da Computação

17 2012-2

#### Desempenho de Protocolos para Barramentos

- Tipos de faltas nas caches:

- ▷ capacidade (mais significativa)

- ▷ conflitos

ci212 — paralelismo (ii)

- ▷ compulsórias

- ▷ coerência  $(4^{\circ} C)$

- Faltas por coerência

são faltas causadas pelo protocolo de coerência

#### • Falso compartilhamento

#### ▷ a unidade de coerência é um bloco de cache

blocos grandes ( $\geq$ 32 pals) para amortizar custos de comunicação e etiquetas

pode ocorrer que um bloco inteiro seja compartilhado, mas palavras individuais não são compartilhadas

tráfego adicional desnecessário 16

2012-2