### Arquitetura II

Cl086 – Tópicos em Arquitetura de Computadores Cl702 – Arquitetura de Computadores

Roberto Hexsel roberto@inf.ufpr.br www.inf.ufpr.br/roberto/CI086.html

LIEPR Dinf BCC

Arquitetura II — introdução

2007-1

### Por que estudar Arquitetura?

HEPR Dinf RCC

Arquitetura II — introdução

2007-1

#### Por que estudar Arquitetura?

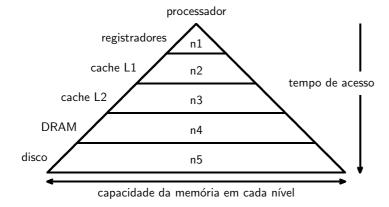

- ser um programador competente: usar caches e memória virtual de forma vantajosa;

- aprender algoritmos e técnicas para alta velocidade: tirar proveito da hierarquia de memória;

- usar bem recursos da máquina: idem com relação a E/S, segmentação;

- poder trabalhar com eletrônica embarcada:

mercado novo e com poucos programadores competentes;

- entender artigos das revistas da ACM, IEEE;

- e, principalmente, ser feliz a vida é de vocês...

### **Bibliografia**

texto:

Computer Architecture: A Quantitative Approach, H&P-QA J L Hennessy e D A Patterson, 3a Ed, Morgan Kaufmann, 2003. cuja tradução ruim é

**Arquitetura de Computadores – uma abordagem quantitativa**, J L Hennessy e D A Patterson, 1a Ed, Campus, 2003,

textos auxiliares:

Computer Organization and Design, P&H-COD D A Patterson e J L Hennessy, 3a Ed, Morgan Kaufmann, 2005 existe tradução da segunda edição

HEPR Dinf RCC

Arquitetura II — introdução 2007

#### **Programa**

- ★ Tendências tecnológicas (1) texto em www.\*://roberto/CI702.html

- ★ avaliação de desempenho (1)

- ★ conjuntos de instruções MIPS64 (2) TODOS DEVEM ESTAR COM O LIVRO!

- ★ revisão pipelines, processadores super-escalares (3)

- ★ paralelismo no nível de instrução, hw e sw (4)

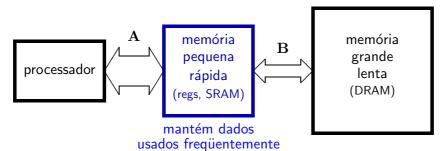

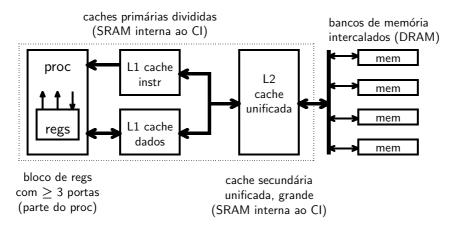

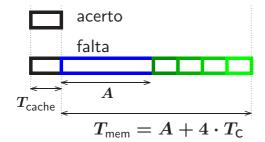

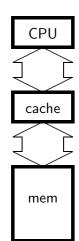

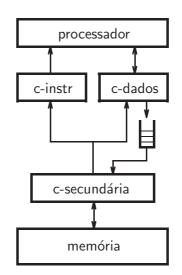

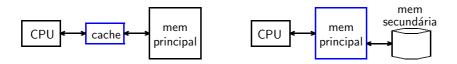

- \* hierarquia de memória, caches, mem virtual (4)

- ★ 03mai prova

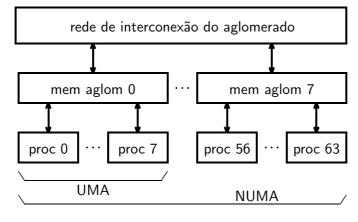

- \* multiprocessadores, mem logicamente compartilhada (4)

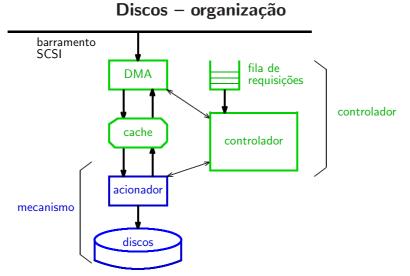

- ★ sistemas de E/S, discos (2)

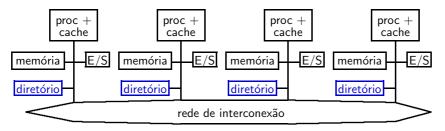

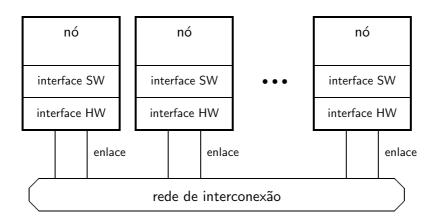

- ★ multicomputadores e clusters, mem logicamente distribuída (2)

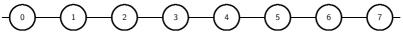

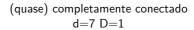

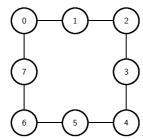

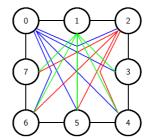

- \* redes diretas (2)

- ★ 21jun prova e 04jul entrega do trabalho

- ★ 03jul final

HEPR DInf RCC

Arquitetura II — introdução

#### Material adicional para o curso

2007-1

http://www.inf.ufpr.br/roberto/CI702.html http://www.inf.ufpr.br/roberto/CI086.html /public/soft/linux/simplescalar ~roberto/ci702

lista de e-mail em roberto-tac@inf.ufpr.br

não guardem este endereço em máquinas com uindous

### Organização de Computadores

#### Modelo de Von Newman

- computador com programa armazenado (1945)

- memória é um vetor de bits

- \* interpretação dos bits definida pelo arquiteto e programador/compilador

- parte da memória contém instruções

- parte da memória contém dados

HEDR DIM RCC

Arquitetura II — introdução 2007-

### Definição de Arquitetura de Computadores

arquitetura do conjunto de instruções (CdI): conjunto de instruções e registradores visíveis ao programador Instruction Set Arquitecture = ISA

2. organização:

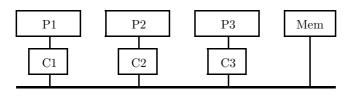

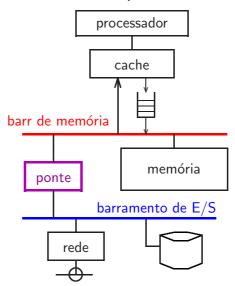

blocos como sistema de memória, barramentos, CPU mais de uma implementação de mesmo conjunto de instruções (AMD e Intel, 80{,1,2,3,4,5,6}86)

3. hardware:

tecnologia de implementação, circuitos integrados (CMOS vs NMOS), pipelining vs multi-ciclo

#### Arquitetura engloba todos os três aspectos

HEDR DIAFRCC

### Requisitos a serem atendidos pelo arquiteto I

ÁREA DE APLICAÇÃO:

Arquitetura II — introdução

usos do computador

**desktop** desempenho balanceado para diversas tarefas; sistemas interativos com gráficos, vídeo e áudio;

**servidor de computação científica** alto desempenho com operações de ponto flutuante e gráficos;

servidor comercial alto desempenho com bancos de dados e sistemas transacionais; confiabilidade, disponibilidade e escalabilidade;

embutido suporte a aplicações específicas;

baixo custo e pequeno consumo de energia

IIFPR Dinf RCC 9

#### Requisitos a serem atendidos pelo arquiteto II

COMPATIBILIDADE DE SOFTWARE:

software pré-existente

**nível de linguagem de programação** maior flexibilidade; novo compilador?

**compatibilidade nos binários** ISA completamente definido; pouca flexibilidade mas sem investimentos em software novo.

HEPR Dinf RCC 10

Arquitetura II — introdução

2007-1

### Requisitos a serem atendidos pelo arquiteto III

SUPORTE A SISTEMA OPERACIONAL:

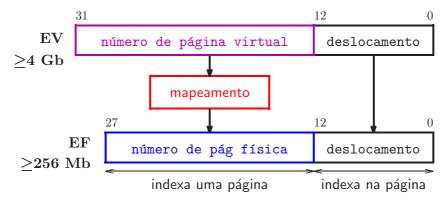

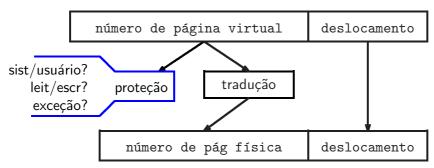

**tamanho do espaço de endereçamento** importantíssimo!! pode limitar aplicabilidade;

ightarrow EdE cresce  $\geq 1/2$  bit aa

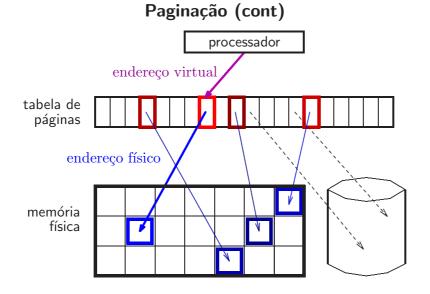

**gerenciamento de memória** necessário para SOs modernos; paginado ou segmentado;

**proteção** usos diferentes por SO e usuários; proteção à páginas ou a segmentos.

HEPR Dinf RCC 1

Arquitetura II — introdução 2007-

# Requisitos a serem atendidos pelo arquiteto IV

Padrões: requeridos pelo mercado

ponto flutuante formatos e aritmética: IEEE754;

barramentos dispositivos de E/S: PCI, SCSI;

sistema operacional Unix, Windows, PalmOS;

redes suporte a tecnologias distintas (Ethernet, Infiniband);

linguagens de programação linguagem de alto nível afeta projeto do conjunto de instruções.

IIFPR Dinf RCC 12

### **Tecnologias Fundamentais**

- 1. tecnologia de semicondutores: microprocessadores CMOS

- 2. tecnologia de semicondutores: memória dinâmica (DRAM)

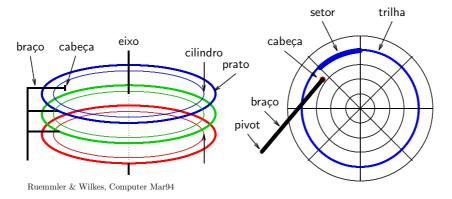

- 3. tecnologia de armazenamento: discos magnéticos

- 4. tecnologia de interconexão: redes locais

HEPR Disf RCC 11

Arquitetura II — introdução 2007-1

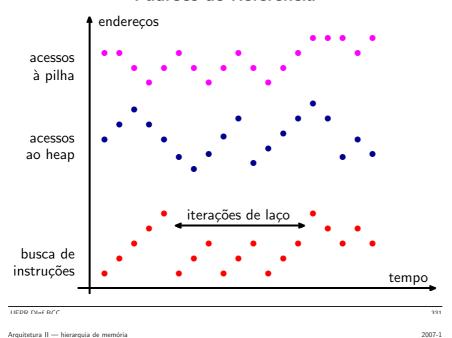

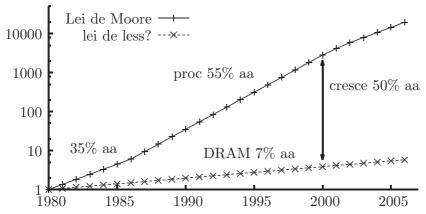

### Tendências da Tecnologia I

### Tecnologias de implementação fundamentais 1- Circuitos Integrados para CPUs

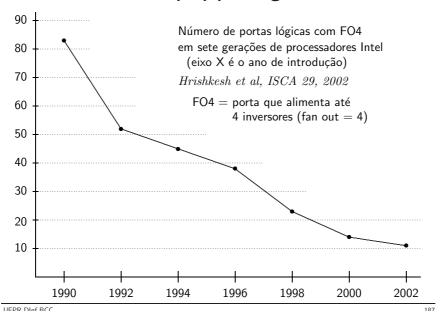

núm de transistores cresce  $\approx 35\%$  aa 4X em 4 anos

tamanho do Cl aprox 10 a 20% aa lado do retângulo

efeito combinado núm transistores/Cl cresce ≈55% aa

Ver fabricação de circuitos integrados em www.intel.com→ museum e em P&H-COD

HEPR Dist RCC 14

Arquitetura II — introdução 2007-1

# Fotografia de um CI do Pentium IV

### Wafer de 8" com 564 MIPS R20K

HEPR DInf RCC 16

# Arquitetura II — desempenho Revisão

#### Arquitetura é:

```

conjunto de instruções + organização + hardware especif abstrata + especif refinada + concreta

```

| Tendências da Tecnologia |              |                |  |

|--------------------------|--------------|----------------|--|

|                          | capacidade   | velocidade     |  |

| lógica                   | 2x em 3 anos | 2x em 3 anos   |  |

| DRAM                     | 4x em 3 anos | 2x em 10 anos  |  |

| disco                    | 4x em 3 anos | 2x em 10 anos  |  |

| processador              | _            | 2x em 1.5 anos |  |

HEPRING RCC 11

Arquitetura II — desempenho 2007-1

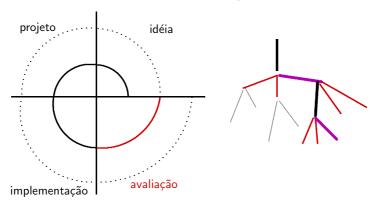

## Processo de Projetar

Processo iterativo: idéia  $\Longrightarrow$  implementação  $\Longrightarrow$  avaliação  $\Longrightarrow$  re-projeto ...

avaliação geralmente implica em descartar idéias ruins

LIFPR Dinf RCC

### Ferramentas para Avaliação de Desempenho

- sistema: programas de teste, rastros (traces)

- hardware: custo, atrasos, área, potência

- simulação nos níveis: Cdl, register transfer, portas, circuitos

- Teoria de Filas

- Regras de projeto

- princípios fundamentais

- Leis (de Moore, de Amdahl, et alli)

HEPR Dist RCC 10

Arquitetura II — desempenho

2007-1

### Avaliação de Desempenho

QUAL É O MELHOR AVIÃO?

| avião    | capacidade | alcance | veloc  | produção |

|----------|------------|---------|--------|----------|

|          | [p]        | [km]    | [km/h] | [p*km/h] |

| B-737    | 101        | 1008    | 957    | 96657    |

| B-747    | 470        | 6640    | 976    | 458720   |

| Concorde | 132        | 6400    | 2160   | 285120   |

| DC-8     | 146        | 13952   | 870    | 127020   |

O que importa são DESEMPENHO e CUSTO

LIEDE DIN ERC 20

Arquitetura II — desempenho 2007-1

### Métricas para Avaliação de Desempenho

aplicação respostas por hora; operações por segundo

linguagem produtividade do programador (?)

compilador qualidade do código gerado

ISA instruções por segundo (MIPS ou MFLOPS)

circ de dados megaBytes por segundo

unid. funcionais ciclos/operações por segundo

portas, fios ciclos por segundo

### Desempenho (i)

$$\mathsf{desempenho}_X \stackrel{\triangle}{=} \frac{1}{\mathsf{tempo}\,\,\mathsf{exec}_X}$$

$X \notin \boldsymbol{\mathcal{M}} \text{ vezes mais rápido que } Y \text{ se} \\ \text{o tempo de execução de } Y \notin \boldsymbol{\mathcal{M}} \text{ vezes mais longo que o de } X$

$$\frac{\mathsf{desempenho}_{X}}{\mathsf{desempenho}_{Y}} = \frac{\mathsf{tempo}\ \mathsf{exec}_{Y}}{\mathsf{tempo}\ \mathsf{exec}_{X}} = \mathcal{M}$$

Desempenho tem unidade de "coisas" por segundo; maior desempenho é melhor!

HEPR Dinf RCC 22

Arquitetura II — desempenho 2007-

### Desempenho (ii)

$$\frac{\mathsf{desempenho}_X}{\mathsf{desempenho}_Y} = \frac{\mathsf{tempo}\ \mathsf{exec}_Y}{\mathsf{tempo}\ \mathsf{exec}_X} = \mathcal{M}$$

#### Exemplo:

Máquina A executa programa em 10 segundos; máquina B executa mesmo programa em 15 segundos. Quanto A é melhor que B ?

$$\frac{\mathsf{desempenho}_A}{\mathsf{desempenho}_B} = \frac{\mathsf{tempo}\ \mathsf{exec}_B}{\mathsf{tempo}\ \mathsf{exec}_A} = \frac{15}{10} \Rightarrow 50\%$$

HEPR Dist RCC 23

Arquitetura II — desempenho

2007-1

#### Avaliação de Desempenho

- tempo de resposta, tempo decorrido [s/tarefa]

- tempo de CPU (usuário + sistema) [s]

- ciclo de relógio [ns] frequência do relógio [GHz]

- vazão/produção (throughput) [tarefas/s]

desempenho do sistema = tempo decorrido (sem carga) desempenho de CPU = tempo de CPU dedicado ao usuário

desempenho de pico  $\mathrm{NUNCA}$  é atingido na prática desempenho de pico  $\gg$  desempenho sustentado

### Equação do Desempenho (i)

tempo de CPU

$$=$$

ciclos da CPU  $\times$  ciclo de relógio

$$= \frac{\text{ciclos da CPU}}{\text{freq de relógio}}$$

ciclos da CPU = núm de instr

$$\times$$

núm de ciclos por instr

$$CPI \stackrel{\triangle}{=} ciclos \ por \ instrução$$

HEPR Dinf RCC 2

Arquitetura II — desempenho

### Equação do Desempenho (ii)

tempo de CPU = núm de instr

$$\times$$

CPI  $\times$  ciclo de relógio =  $\frac{\text{núm de instr} \times \text{CPI}}{\text{freq de relógio}}$

esta é a equação mais importante do semestre!

HEPR Dinf RCC 2

Arquitetura II — desempenho 2007-

#### Equação do Desempenho (iii)

#### Exemplo:

Programa executa na máquina A em 10s com relógio de 100MHz. Queremos máquina B que execute mesmo programa em 6s. Por causa da mudança no projeto da CPU, máquina B vai usar 1.2 vezes mais ciclos de relógio que A. Qual o relógio de B?

tempo de

$$\mathsf{CPU}_A = \frac{\mathsf{ciclos}\;\mathsf{da}\;\mathsf{CPU}_A}{\mathsf{freq}\;\mathsf{de}\;\mathsf{relógio}_A}$$

$$10s = \frac{\mathsf{ciclos}\;\mathsf{da}\;\mathsf{CPU}_A}{100\times10^6}$$

$\Rightarrow \;\#\mathsf{ciclos}\;\mathsf{da}\;\mathsf{CPU}_A = 1000\times10^6$

$$\begin{array}{ll} \text{tempo de CPU}_B &=& \frac{1.2*\text{ciclos da CPU}_A}{\text{freq de relógio}_B} \\ &\Rightarrow& \text{freq de relógio}_B = \frac{1.2*1000\times10^6}{6s} \\ &\Rightarrow& \text{freq de relógio}_B = 200\times10^6 \\ \\ \text{ganho de } \frac{10}{6} = 0.67 &\Rightarrow& \text{freq de relógio } 100\% \text{ maior} \end{array}$$

Exemplo: Programa executa na máquina A em 10s com relógio de 100MHz. Queremos máquina B que execute mesmo programa em 6s. Por causa da mudança no projeto da CPU, máquina B vai usar 1.2 vezes mais ciclos de relógio que A. Qual o relógio de B?

HEPR Dist RCC 23

Arquitetura II — desempenho 2007-

### Equação do Desempenho (iv)

tempo de CPU

$$= \mathcal{N} \times \text{CPI} \times \mathcal{R}$$

núm instr $\times \text{CPI} \times \text{período do relógio}$

$$\mathsf{CPI} \ = \ \sum_{j}^{n} \mathsf{CPI}_{j} imes \mathsf{F}_{j}$$

onde  $\mathsf{F}_{j} = \mathcal{I}_{j}/\mathcal{N}$   $\mathsf{F}_{j}$  é a freqüência da instrução  $\mathcal{I}$

HEPR Dist RCC 20

# Equação do Desempenho (v)

$$\mathsf{CPI} = \sum_{j=0}^{n} \mathsf{CPI}_{j} \times \mathsf{F}_{j}$$

| instr   | freq[%] | ciclos | $CPI_j$ |

|---------|---------|--------|---------|

| ALU     | 40      | 1      | .40     |

| load    | 25      | 3      | .75     |

| store   | 10      | 3      | .30     |

| desvios | 25      | 2      | .50     |

|         |         | total  | 1.95    |

#### **Fatores Determinantes**

tempo de CPU = núm de instr $\times$  CPI  $\times$  ciclo de relógio

| tempo de CPU          | desempenho do sistema            |

|-----------------------|----------------------------------|

| núm de instruções     | compilador & processador         |

| CPI                   | organização e arquitetura da CPU |

| freqüência de relógio | tecnologia de CIs & arquitetura  |

HEPR Dist RCC

Arquitetura II — desempenho

#### Administrativamente falando...

Todos já estão com o livro?

Mestrandos já estão com os artigos?

Ler:

How not to lie with statistics: the correct way to summarize benchmark results, Fleming & Wallace, Comm ACM 29(3), Mar 1986

Characterizing computer performance with a single number, J E Smith, Comm ACM 31(10), Oct 1988

HEPR Dinf RCC 2'

Arquitetura II — desempenho 2007-1

#### Medidas de desempenho

MIPS = milhões de instruções por segundo

MIPS =

$$\frac{\text{num de instr}}{\text{tempo decorrido} \times 10^6}$$

$$= \frac{\text{freq de relógio}}{\text{CPI} \times 10^6}$$

#### **Problemas**

- independente do conjunto de instruções (RISC/CISC)

- varia para programas na mesma máquina (int×PF)

- pode variar na proporção inversa ao desempenho

### Medidas de desempenho

MFLOPS = milhões de instr de ponto flutuante p/s

MFLOPS =

$$\frac{\text{núm de instr de pto flutuante}}{\text{tempo decorrido} \times 10^6}$$

#### **Problemas**

- independente do conjunto de instruções (Cray/68882)

- varia para programas na mesma máquina (soma×div)

- média ponderada de custo de instruções:  $soma(a,b) \propto 1$   $seno(x) \propto 8$

HEPR Dinf RCC

Arquitetura II — desempenho

2007-1

### Medir desempenho com programas de teste

**programas simples:** quicksort, números primos simples de implementar, fora da realidade

programas sintéticos: Dhrystone, Whetstone simples de implementar, não são código usável

núcleos de programas: SPEC, Livermore Loops

fáceis de medir, não testam sistema de forma realista

programas de verdade: gcc, LaTeX, Spice

mistura deve refletir uso "normal" (browser?)

HEPR Dinf RCC 34

Arquitetura II — desempenho

2007-1

### Medindo desempenho - SPEC

- primeiro conjunto em 1989

- ★ 10 programas produzem um só número: SPECmarks

- segundo conjunto em 1992

- \* SPECint92 com 6 programas com inteiros

- $\star$  SPECfp92 com 14 programas com ponto flutuante

- terceiro conjunto em 1995

- ★ SPECint95 com 8 programas com inteiros

- ★ SPECfp95 com 10 programas com ponto flutuante

- \* conjunto caduca em três anos

- \* versão base com mesmas flags de compilação (todos programs)

- quarto conjunto em 2000

- ★ CINT2000 com 11 programas com inteiros (C e C++)

- $\star$  CFP2000 com 14 programas com ponto flutuante (fortran{77,90}, C)

### Comparação de resultados

|            | máq ${\cal A}$ | máq <i>B</i> |

|------------|----------------|--------------|

| prog 1 [s] | 1              | 10           |

| prog 2 [s] | 1000           | 100          |

| total [s]  | 1001           | 110          |

com programa 1,  $\mathcal{A}$  é 10 vezes mais rápido que  $\mathcal{B}$  com programa 2,  $\mathcal{B}$  é 10 vezes mais rápido que  $\mathcal{A}$  erm...

Média Aritmética =

$$\frac{1}{n}\sum_{i=1}^n \mathsf{Tempo}_i$$

${\cal B}$  é 1001/110=9.1 vezes mais rápido que  ${\cal A}$

HEPR Dist RCC 37

Arquitetura II — desempenho 2007-1

### Resumindo desempenho com um só Número

• média aritmética (ponderada) segue tempo de execução:

$$\sum T_i/n$$

ou  $\sum (p_i \cdot T_i)$

• média harmônica (ponderada) de taxas (MIPS/MFLOPS) segue tempo de execução:

$$n/\sum (1/R_i)$$

ou  $n/\sum (p_i\cdot R_i)$

- tempo de execução normalizado é útil para comparações de escalabilidade (máquina-A é X vezes mais rápida que modelo-base)

- para tempo de execução normalizado, deve usar média geométrica:

$$(\prod T_i/N_i)^{1/n}$$

HEPR Dinf RCC 3

Arquitetura II — desempenho 2007-1

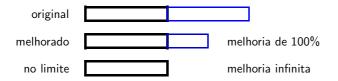

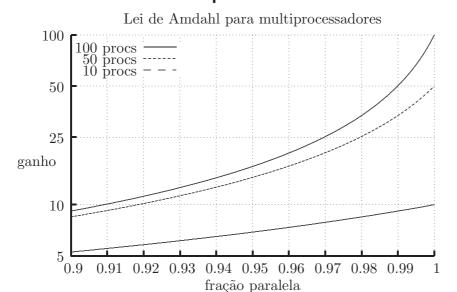

# Lei de Amdahl (i)

Tempo de execução após melhoria = (tempo de execução afetado / quanto melhorou) + tempo de execução não-afetado

esta também é importante

#### Exemplo:

programa executa em 100s, multiplicações consomem 80% do tempo total. Quanto devo melhorar o circuito multiplicador se quero tempo total em 20s ?

$$20 = 80/n + 20$$

Idem se quero tempo total em 40s ?

$$40 = 80/n + 20$$

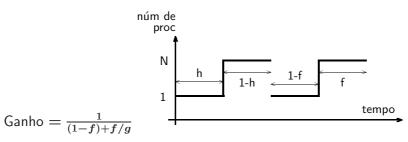

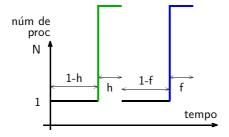

### Lei de Amdahl (ii)

$$\begin{array}{ll} \mathsf{Ganho}_{\mathsf{total}} & = & \frac{\mathsf{Tempo}_{\mathsf{orig}}}{\mathsf{Tempo}_{\mathsf{melhor}}} \\ \\ & = & \frac{1}{(1 - \mathsf{Frac}_{\mathsf{melhor}}) + (\mathsf{Frac}_{\mathsf{melhor}} \slash \mathsf{Ganho}_{\mathsf{melhor}})} \end{array}$$

LIEPR Dinf RCC

Arquitetura II — desempenho 2007-1

### Lei de Amdahl (iii)

#### Exemplo:

programa executa em 100s, multiplicações consomem 80% do tempo total. Melhorando o circuito multiplicador em 50%, qual é o ganho total de velocidade ?

$$\begin{array}{ll} \mathsf{Ganho_{total}} &=& \frac{1}{(1-0.80)+\frac{0.80}{1/0.50}} \\ &=& \frac{1}{0.20+0.80*0.50} \\ &=& \frac{1}{0.60} \approx 67\% \end{array}$$

HEPR Dist RCC

Arquitetura II — conj de instruções 2007-1

#### Resumo

Equação do Desempenho: o que vale é o tempo de execução!

tempo de CPU =

$$\frac{\text{instruções}}{\text{programa}} \times \frac{\text{ciclos}}{\text{instrução}} \times \frac{\text{tempo}}{\text{ciclo}}$$

Lei de Amdahl: o que interessa é o desempenho global!

$$\mathsf{Ganho}_{\mathsf{total}} = \frac{1}{(1 - \mathsf{Frac}_{\mathsf{melhor}}) + (\mathsf{Frac}_{\mathsf{melhor}} \, / \, \, \mathsf{Ganho}_{\mathsf{melhor}})}$$

### revisão: Definição de Arquitetura

- Conjunto de Instruções: visão do programador, compilador

- Organização: visão do projetista do computador

- Implementação I: visão do projetista do processador

- Implementação II: visão do projetista dos circuitos integrados

HEPR Dist RCC 42

Arquitetura II - conj de instruções

2007-1

#### revisão: Equação do Desempenho

tempo de CPU =

$$\frac{\text{instruções}}{\text{programa}} \times \frac{\text{ciclos}}{\text{instrução}} \times \frac{\text{tempo}}{\text{ciclo}}$$

$$|\text{código}| \times \text{CPI} \times |\text{ciclo}|$$

- tamanho do código depende de algoritmo e compilador

- CPI depende do Conj de Instruções e organização da CPU

- ciclo depende da organização e implementação da CPU

- objetivo: minimizar tempo e não termos isolados

HEPR Dinf RCC

Arquitetura II — conj de instruções 2007-1

### Arquitetura ao longo das décadas

| DÉCADA                                             | ARQUITETO ENVOLVE-SE COM                         |               |

|----------------------------------------------------|--------------------------------------------------|---------------|

| 1960                                               | projetar circuitos aritméticos eficientes        |               |

| 1970                                               | projeto de conjunto de instruções [1]            |               |

| 1980                                               | RISC vs CISC, super-escalaridade, compi          | ladores [2]   |

| 1990                                               | espaço de endereçamento dobra (32 $ ightarrow$ 6 | 64 bits)      |

|                                                    | otimização de desvios através de execuçã         | o condicional |

|                                                    | suporte a multi-mídia; operações de pont         | o flutuante   |

| 2000                                               | instruções largas (VLIW)                         |               |

| maior suporte a especulação (execução condicional) |                                                  | ondicional)   |

|                                                    | emulação de 80×86                                | (Transmeta)   |

[1] Maior complexidade para aumentar produtividade dos programadores

[2] If a compiler cannot generate it, desktop and server programs

generally won't use it. H&P QA pg 91

### Conjunto de Instruções

#### Recorte:

- operações

- operandos

- endereçamento de operandos

- codificação

- implementação

Instruction Set Architecture  $\longrightarrow$  ISA = parte visível ao programador e ao compilador  $\longleftrightarrow$  interface

HEPR Dist RCC

Arquitetura II — conj de instruções

2007-1

### Conjunto de Instruções ≡ interface hw-sw

#### CDI especifica a funcionalidade do processador

- quais operações ele suporta

- quais mecanismos de armazenamento suporta e sua utilização

- como programador/compilador define programas a executar

Estudo de CDIs é a parte de arquitetura deste curso; restante é micro-arquitetura

HEPR Dist RCC 47

Arquitetura II — conj de instruções

2007-1

#### Conjunto de Instruções ≡ interface hw-sw

#### Interface bem projetada:

- sobrevive a muitas implementações (portabilidade, compatibilidade)

- é usada de muitas maneiras (generalidade)

- provê funcionalidade conveniente aos níveis acima

- permite implementação eficiente nos níveis abaixo

### Receita para um "bom" Conjunto de Instruções

#### implementabilidade

permite implementações numa faixa de preço/desempenho

DEVE permitir implementações de alto desempenho

#### programabilidade

deve facilitar expressão de programas pelo programador/compilador

**compatibilidade** para o futuro e com o passado implementabilidade e programabilidade através de gerações: deve garantir que todo sw existente execute x86: 8086,286,386,486,Pentium{,Pro,II,III,4}

Estas são as 3 "-idades" de um CdI

HEPR Dist RCC

Arquitetura II — conj de instruções 2007-1

#### ISA - operações

| tipo                   | exemplo                |

|------------------------|------------------------|

| aritmética e lógica    | add, sub, and, sll     |

| transferência de dados | move, load             |

| controle               | branch, jump, call     |

| sistema                | syscall, trap          |

| ponto flutuante        | fadd, fmul, fdiv, sqrt |

| decimal                | addd, convert          |

| string                 | move, comp             |

| multimidia 2D, 3D      | MMX/SSE                |

LIEPR DIM RCC St

Arquitetura II — conj de instruções 2007-

### ISA - operações

10 instruções do x86 mais populares em 5 programas SPECint95:

| $\operatorname{ord}$ | instrução    | % total |              |

|----------------------|--------------|---------|--------------|

| 1                    | load         | 22      |              |

| 2                    | desv cond    | 20      | 1/5          |

| 3                    | compare      | 16      |              |

| 4                    | store        | 12      | Id+st 	o 1/3 |

| 5                    | add          | 8       |              |

| 6                    | and          | 6       |              |

| 7                    | sub          | 5       |              |

| 8                    | move reg-reg | 4       | por que?     |

| 9,10                 | call+ret     | 1 + 1   |              |

|                      | total        | 96      |              |

Amdahl legisla: estas devem ser otimizadas

HEPR Dinf RCC 5:

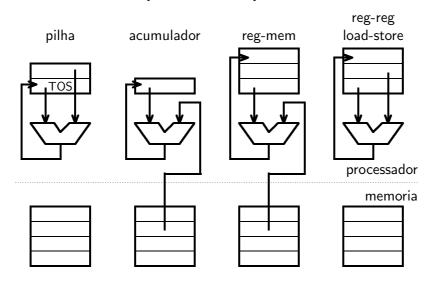

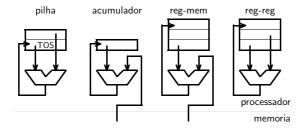

### ISA - operandos

- Localização dos operandos

- \* no processador

- \* em memória

- Quantos bits são necessários para identificar um operando?

- \* no processador

- \* em memória

- Quanto tempo é necessário para acessar um operando?

- \* no processador

- \* em memória

HEPR Dist RCC 55

Arquitetura II — conj de instruções

2007-1

### ISA - operandos no processador

HEPR Dinf RCC

Arquitetura II — conj de instruções

2007-1

#### ISA - operandos no processador

Operandos no processador: acesso rápido & identificação compacta

- Acumulador

- \* código compacto (endereço implícito)

- \* hardware simples

- \* tráfego elevado de/para memória

- Pilha

- \* código compacto (endereço do topo da pilha implícito)

- Registradores

- \* registradores devem ser identificados

- \* espaço de nomes adicional (variáveis em memória e registradores)

- \* menos acessos à memória

- \* maior velocidade porque regs. são mais rápidos que memória

### ISA - operandos no processador

código para computar C = A + B

| PILHA  | ACUMUL  | REG-MEM     | REG-REG      |

|--------|---------|-------------|--------------|

| push A | load A  | load R1,A   | load R1,A    |

| push B | add B   | add R3,R1,B | load R2,B    |

| add    | store C | store R3,C  | add R3,R1,R2 |

| pop C  |         |             | store R3,C   |

LIEPR Dinf BCC

Arquitetura II - conj de instruçõe

2007-1

### ISA - operandos para operações de ULA

- Instruções da ULA combinam operandos

- número de operandos é implícito:

- \* dois: r1 ← r1 OP r2 código denso destrutivo porque sobre-escreve destino assimétrico (A-B, A/B)

- \* três: r1 ← r2 OP r3

- operandos em registradores ou em memória

- \* registrador + memória (IBM, x86)

NÃO ORTOGONAL

\* reg + reg (RISCs, Cray)

ortogonal com load/store

ortogonal,

\* qualquer combinação (VAX)

instr com tamanho variável

HEPR Dinf RCC

Arquitetura II — conj de instruções

2007-1

#### ISA - de volta a Lilliput

Ordem dos bytes nas palavras

• big endian: byte com endereço xxxx002 na posição mais significativa de uma palavra de 32 bits Motorola (powerPC), IBM (r6000), SPARC

| end byte | MS |   |   | ms |

|----------|----|---|---|----|

| 0        | 0  | 1 | 2 | 3  |

| 4        | 4  | 5 | 6 | 7  |

• little endian: byte com endereço xxxx002 na posição menos significativa de uma palavra de 32 bits DEC (alpha), Intel (x86)

| end byte | MS |   |   | ms |

|----------|----|---|---|----|

| 0        | 3  | 2 | 1 | 0  |

| 4        | 7  | 6 | 5 | 4  |

ambos – MIPS (e powerPC)

### ISA - alinhamento de operandos

• Palavras tem "tamanho natural":

byte, half-word, word, doubleword float, double, quadword

• Operando alinhado pelo tamanho natural se

#### endereço MOD tamanho = 0

$\star$  palavra alinhada: ender mod 4 = 0 1024, 1028, 102c, 1030,...  $\mod 4$  porque palavra tem tamanho de 4 bytes

★ palavra desalinhada ender mod  $4 \neq 0$

1025 ou 1026 ou 1027

TIEPR DINFRCC 5

Arquitetura II — conj de instruções

2007-1

#### ISA - alinhamento de operandos

- sem restrições

- ★ software mais simples

- $\star\,$  hardware deve detectar e fazer  $\geq 2$  referências à memória

- ★ lógica complexa; tempo extra em todas as instruções (pior caso)

- \* dificulta adiantamento de loads no pipeline

- com restrições

- ★ software deve garantir alinhamento

- \* hardware verifica e provoca excessão se for o caso

- $\star$  adiantamento de loads mais simples

- mais ou menos

- \* mais de uma instrução para acessos desalinhados (load-half)

- \* compilador ajuda no alinhamento

- ★ hardware verifica e provoca excessão se for o caso

HEPR Dinf RCC

Arquitetura II — conj de instruções

2007-1

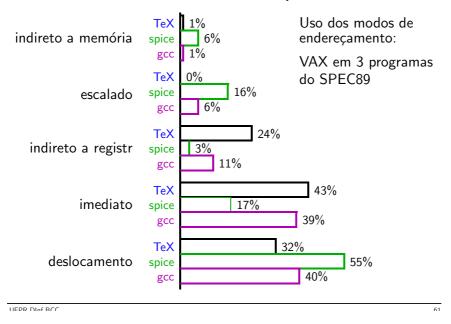

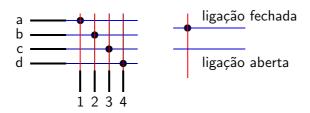

### ISA - modos de endereçamento

| MODO                   | ENDER EFETIVO    | EXEMPLO              |

|------------------------|------------------|----------------------|

| a registrador          | R                | add r4,r3            |

| imediato               | imed             | add r4,#8            |

| deslocamento           | M[R+imed]        | add r4,100(r1)       |

| indireto a registrador | M[R]             | add r4,(r1)          |

| indexado               | $M[R_i {+} R_j]$ | add $r3$ , $(r1+r2)$ |

| absoluto               | M[imed]          | add r1,(1001)        |

| indireto a memória     | M[ M[R] ]        | add r1,@(r3)         |

| auto-incremento        | M[R]; R += d     | add $r1,(r2)+$       |

| auto-decremento        | R -= d; M[R]     | add r1,–(r2)         |

| escalado               | $M[R_i + R_j*d]$ | add r1,100(r2)[r3]   |

Apenas absoluto e indireto a registrador são fundamentais; outros podem ser derivados destes

Arquitetura II - conj de ins

2007-1

### ISA - modos de endereçamento

ISA - modos de endereçamento

- Distância dos deslocamentos (LD e ST)

- \* 16 bits cobre 99% dos casos (dist  $\leq \pm$  32K bytes/pals) Alpha (SPEC CINT2000 e CFP2000)

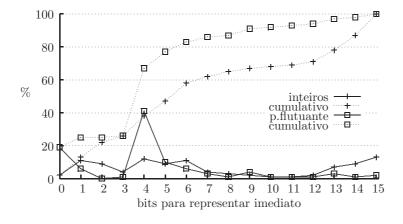

- Uso de imediatos (tamanho das constantes)

- \*~1/5 a 1/4 das instruções de ULA e movimentação de dados usam constantes

- $*\approx 90\%$  das constantes são representadas em  $\leq 16$  bits instruções suportam constantes de 16bits (como representa maiores?)

- \* 20 a 30% das constantes são negativas

HEPR DInf RCC

Arquitetura II — conj de instruções 2007-1

# ISA - modos de endereçamento

Uso de imediatos: Alpha SPEC CINT2000 e CFP2000 1/5-1/4 das instr de ULA e de movim de dados usam constantes

#### Administrativamente falando...

- Avaliação:

- \* BCC

- $\star$  2 provas 35% + 35%

- ★ trabalho 20%

- \* participação nas aulas de exercícios 10%

- \* Mestrado

- $\star$  2 provas 30% + 30%

- ★ trabalho 20% (entrega na semana das finais)

- \* participação nas aulas de exercícios 20%

- 5 aulas de exercícios

- ★ listas distribuídas na aula

HEPR Dinf RCC

Arquitetura II — conj de instruções

2007-1

#### Administrativamente falando...

Todos devem ler o artigo sobre o Cray-1 para a próxima aula The CRAY-1 Computer System, R M Russel, CACM 21(1), Jan 78

#### instruções vetoriais:

```

• addv v1,v2,v3 # for (i=0;i<64;i++) v1[i]=v2[i]+v3[i];

```

• encadeamento (chaining):

"saída" do ldv passa direto para muliv, para addv e para stv

HEPR Dinf RCC

Arquitetura II — conj de instruções

2007-1

#### ISA - controle de fluxo de execução

- Cada instrução é auto-contida (≠ if-then-else, do-until)

- Seqüência de execução de instruções é determinada pelo PC

- \* execução seqüencial: PC++

- \* instruções mudam conteúdo do PC explicitamente: PC ← ENDER

- Aspectos importantes:

- \* desvios condicionais (toma desvio ou segue seqüencialmente)

- \* determinação do endereço de destino

- \* ligação para endereço de retorno de funções

- \* salvamento de estado

- \* interface com sistema operacional

Tipos de instruções de controle:

desvios condicionais (desvia ou prossegue)

saltos incondicionais

chamada de função

geralmente incondicionais

necessita ligação para endereço de retorno

pode salvar estado (registradores)

retorno de função

\* geralmente incondicionais

\* retorno indireto através do endereço de ligação

\* pode salvar estado (registradores)

IIEDR Dief RCC 67

Arquitetura II — conj de instruções 2007-1

### ISA - controle de fluxo de execução

Tipos de instruções de controle:

• chamadas de sistema syscall, trap

\* semelhante à chamada de função

\* endereço de destino definido no opcode

\* atravessa fronteira de proteção

• retorno de chamada de função reti

\* semelhante ao retorno de função

\* opcode diferente da chamada

\* atravessa fronteira de proteção

Arquitetura II — conj de instruções

HEDRING RCC 69

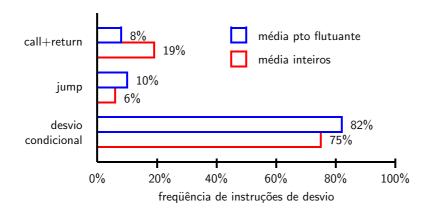

### ISA - controle de fluxo de execução

Tipos de desvios: Alpha SPEC CINT2000 e CFP2000

Tipos de mudança no fluxo:

- condicional ou incondicional

- salva conteúdo do PC

- o endereço de destino endereço fixo (imediato ou PC+imediato) definido em tempo de execução (registrador)

```

HEPR Ninf RCC 70

```

Arquitetura II - conj de instruções

2007-1

2007-1

### ISA - controle de fluxo de execução

- Mecanismos de decisão de desvios:

- \* registrador de status (condition code)

$PC \Leftarrow (R1>R2 ? PC+desloc : PC)$

operação de ALU no caminho crítico da resolução do

desvio

Arquitetura II - conj de instruções

\* registrador de condição (CC = condition code register)

$R1 \leftarrow (R2 - R3) \text{ mudaCC}$

$PC \leftarrow (CC ? PC + desloc : PC)$

necessita estado adicional (CC)

dificulta reordenação de código (pelo efeito colateral)

\* registrador de uso geral

$R1 \leftarrow (R2 > R3)$

$PC \leftarrow (R1>0 ? PC+desloc : PC)$

pouco estado adicional

usa registrador inteiro para poucos bits

HEPR Dist RCC

### ISA - controle de fluxo de execução

Mecanismos para especificar endereço de destino:

• endereço arbitrário como load/store

```

PC \Leftarrow PC + (R1 + desloc)

```

versátil e ortogonal

mais demorado para decodificar

executa desvio e computa destino em estágios separados

do pipeline (muda PC na busca e computa ender em exec)

Mecanismos para especificar endereço de destino:

• relativo ao PC (deslocamento em imediato)

PC ← (PC+desloc)

código independente de posição facilita ligação

destino pode ser computado no estágio de busca/decodificação imediato com 12 bits cobre 99% dos casos (MIPS)

$(\mathsf{dist} \leq \pm \ \mathsf{2K} \ \mathsf{pals})$

imediato com 16 bits cobre 99,5% dos casos (ALPHA)

(dist  $\leq \pm$  32K pals)

MAS endereço de destino não pode ser muito distante

HEPR DInf RCC

Arquitetura II — conj de instruções

2007-1

### ISA - controle de fluxo de execução

Mecanismos para especificar endereço de destino:

• indireto a registrador (endereço em registrador)

$PC \Leftarrow R1$

código compacto

destino a qualquer distância

destino pode ser computado dinamicamente (retorno de função)

instrução adicional para carregar registrador

muda PC e "calcula" destino em estágios diferentes

endereço implícito no opcode (vetor de syscalls)

necessário para interface com sistema operacional

LIEPR Dief RCC 74

Arquitetura II — conj de instruções

2007-1

### ISA - controle de fluxo de execução

Mecanismos para especificar endereço de ligação/retorno:

- necessário para retorno de função e chamada de sistema

- registrador implícito (R31 no MIPS)

registrador deve ser salvo antes da próxima chamada

- registrador explícito

pouquinho mais de flexibilidade

pilha de chamada de funções

SE pilha é parte da arquitetura complexidade adicional:

instruções tipo push e pop

hardware deve detectar over/under-flow na pilha

Salvar e recompor estado nos saltos/desvios

- que estado salvar

- \* chamadas de função ⇒ registradores (CISCs)

- \* chamadas de sistema \rightharpoonup registradores, PC, flags, PSW

- ISA/hardware não necessita salvar registradores

- \* função que chama salva regs em uso

caller save

\* função chamada salva regs que vai usar

callee save

- ISA/hardware pode salvar registradores

- \* VAX call

- \* pressupõe convenção de chamada/retorno pelo compilador

- processadores recentes n\u00e3o fazem salvamento mas SPARC tem janelas de registradores

HEPR Dinf RCC 7

Arquitetura II — conj de instruções

2007-1

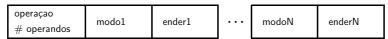

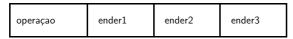

### ISA - codificação das instruções

Tipos de codificação: comprimento variável, fixo e híbrido

Variavel: VAX, Intel x86

Fixo: Alpha, ARM, MIPS, PowerPC, SPARC

| operação | modo1 | ender1 |        |

|----------|-------|--------|--------|

|          | modo1 | ender1 | ender2 |

| operação | modo1 | modo2  | ender  |

Hibrido: IBM 360/370, MIPS16, TI TMS5320c54x

HEPR Dist RCC 7

Arquitetura II — MIPS 2007-1

#### ISA - resumo

Instruction Set Architecture = ISA = parte visível ao programador e ao compilador

operações

operandos

popularidade vs implementação

popularidade vs implementação

• endereçamento de operandos código compacto vs flexibilidade

codificação

código compacto vs decodificação

facilidade de implementação em pipeline

#### revisão: Desempenho

Equação do desempenho: o que interessa é o tempo total!

tempo de CPU =

$$\frac{\text{instruções}}{\text{programa}} \times \frac{\text{ciclos}}{\text{instrução}} \times \frac{\text{tempo}}{\text{ciclo}}$$

$$|\text{código}| \times \text{CPI} \times |\text{ciclo}|$$

Lei de Amdahl: o que interessa é o desempenho global!

$$\mathsf{Ganho}_{\mathsf{total}} = \frac{1}{(1 - \mathsf{Frac}_{\mathsf{melhor}}) + (\mathsf{Frac}_{\mathsf{melhor}} \, / \, \, \mathsf{Ganho}_{\mathsf{melhor}})}$$

HEPR Dist RCC 70

Arquitetura II — MIPS 2007

### revisão: Conjunto de Instruções

- Instruction Set Architecture = ISA

= parte visível ao programador e ao compilador

- contrato entre hardware e software

- simplifica compilador se

- \* ortogonal

- \* regular

- \* facilitar composições

- codificação simples e regular simplifica hardware

- ⋆ operações popularidade vs implementação

- ★ operandos popularidade vs implementação

- ★ endereçamento de operandos código compacto vs flexibilidade

- \* codificação código compacto vs decodificação facilidade de implementação em pipeline

HEPR Dinf RCC

Arquitetura II — MIPS 2007-1

#### Compiladores 0

Função do compilador:

- todos os programas corretos executam corretamente

- maioria dos programas compilados executa rapidamente

- compilação rápida

- suporte a depuração

bloco básico = trecho de código entre desvios

#### Compiladores 0

| estágio       | depende de | função                             |

|---------------|------------|------------------------------------|

| front end     | linguagem  | produz representação intermediária |

| otimizador de | linguagem  | transformação de loops             |

| alto nível    | (pouco)    | integração de funções              |

| otimizador    | máquina    | otimização local e global          |

| global        | (pouco)    | alocação de registradores          |

| gerador de    | máquina    | seleção de instruções              |

| código        | (muito)    | otimização dependente de máquina   |

IIEPP Dief RC

8

Arquitetura II — MIPS

2007

#### Compiladores 0 - estilos de transformação

- otimização no alto nível

- \* efetuada na linguagem de alto nível para uso pelos outros estágios

- otimização local

- \* otimização somente em blocos básicos

- otimização global

- \* otimização que atravessa blocos básicos

- \* transformação de loops

- alocação de registradores

- \* associa registradores com operandos

- otimização dependente do processador

- \* depende da arquitetura

LIEPR DIM RCC 8:

Arquitetura II — MIPS 2007-

#### Compiladores 0 - operações nos estágios

- tradução para representação intermediária

- expansão de funções inlining

- otimização de loops desenrolar; código invariante

- eliminação da variável de indução cálculo de índices

- eliminação de sub-expressões comuns cálculos repetidos

- otimizações de saltos

- propagação de constantes

variável que é constante

- alocação de registradores

- strength reduction mult vs soma+desloca

- escalonamento do pipeline reordenação; branch delay slots

- tradução para linguagem de máquina

Arquitetura II - MIPS

#### Compiladores 0 - do que eles gostam?

- quem escreve um compilador deseja

- \* regularidade simplifica análise de casos

- \* ortogonalidade suporta todas as combinações \* composabilidade primitivas ao invés de soluções

- \* as três permitem operações simples combinadas em operações complexas

- compiladores efetuam análise de casos gigantesca

- \* opções demais dificultam escolhas

- conjuntos de instruções ortogonais quanto a

- \* operações tipos de dados modos de endereçamento

- \* completude

condições de desvio → eq lt uma, ou cond de desvio → eq ne lt gt le ge todas as soluções, mas não só algumas escolhas idiossincráticas

LIEPR Dinf BCC

Arquitetura II - MIPS 2007-1

### Conjunto de Instruções do MIPS

Projeto de RISCs na década de 80 para obter implementação de pipelines num único CI

> Reduced Instruction Set Computers reduced == simples, e não pequeno

- ênfase em

- \* decodificação rápida

- \* instruções com tamanho fixo

- \* codificação regular

- compilador poderia escalonar instruções para execução

- código grande/esparso

LIEPR Dinf BCC

Arquitetura II - MIPS

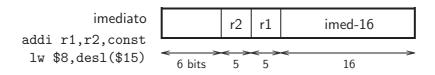

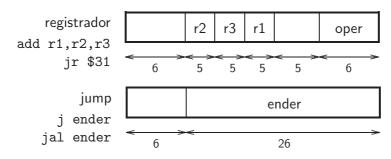

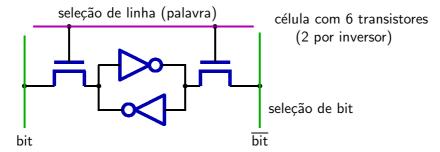

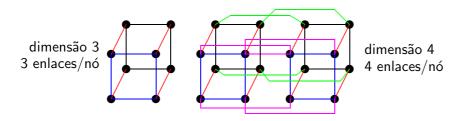

#### MIPS64

- endereços alinhados de 32 bits

- modo de endereçamento é deslocamento load/store

- tipos de dados simples: byte half word doubleword, single double

- registradores

- \* 32 regs de uso geral, de 64 bits (R0 = 0) regs

- \* 32 regs de ponto flutuante de 64 bits regsPF

- \* registrador de status para ponto flutuante

- \* sem registrador de status para inteiros

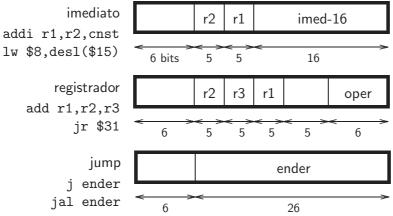

- três formatos de instrução com mesmo tamanho

LIEPR Dinf RCC

### MIPS - modos de endereçamento

| MODO                   | ENDER EFETIVO | EXEMPLO        |

|------------------------|---------------|----------------|

| a registrador          | R             | add r4,r3,r2   |

| imediato               | imed          | add r4,#8      |

| deslocamento           | M[R+imed]     | add r4,100(r1) |

| indireto a registrador | [R]           | jr r4          |

| absoluto               | ender         | j ender        |

HEPR Dinf RCC Arquitetura II — MIPS

2007-1

#### **MIPS**

• transferência de dados

- \* load/store byte/half/word/doubleword

- \* load/store PF single/double

- \* move de-para regs e regsPF

- ULA

- \* add/sub/mult/div

- \* and/or/xor

- \* sll/srl (lógicos), sra (aritmético) deslocamentos

- \* loadHigh (usado para constantes de 32 bits)

HEPR Dinf RCC

Arquitetura II — MIPS

#### **MIPS**

- ponto flutuante

- \* add/sub/mult/div single/double

- \* conversões de-para inteiros

- \* desvios (liga/desliga bits para desvios)

- controle

- $\neq 0$ bits\_PF \* desvios condicionais: =0

\* jump/jr jump-register \* jal jump-and-link-register \* trap/rte return from exception

#### **MIPS**

#### Formatos das instruções

- formato-I

- \* instruções de ALU com imediatos

- \* load e store

- \* desvios condicionais

- \* jump-register

TIEDR Dist RCC

Arquitetura II — MIPS 2007-1

#### **MIPS**

#### Formatos das instruções

- formato-R

- \* instruções de ALU com três operandos

- formato-J

- \* saltos incondicionais

HEPR Dinf RCC

Arquitetura II — MIPS 2007-1

#### **MIPS**

- ullet instruções regulares facilitam decodificação  $\longrightarrow$  hw rápido

- instruções simples facilitam construção do compilador e geração de código → sw rápido

#### Administrativamente falando...

ou

#### filmes imperdíveis para computeiros:

Enigma → ponto de vista dos europeus que quebraram o código U571 → marinheiros/cowboys capturam máquina de codificação assistam aos dois

Quem conseguir, leia *The enigma of inteligence* que é a biografia de Alan Turing, tido como o pai da IA além de muitas outras coisas

HEPR Dist RCC 04

Arquitetura II — MIPS 2007-1

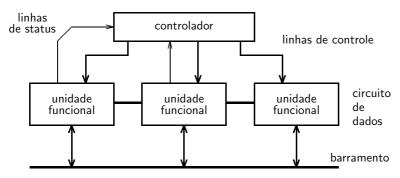

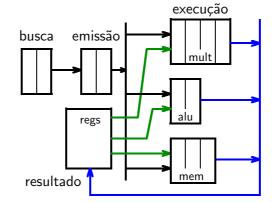

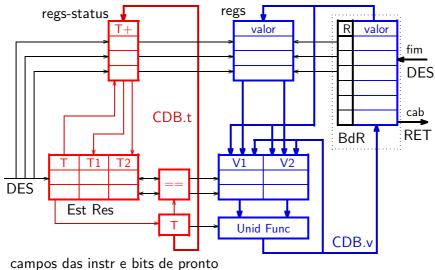

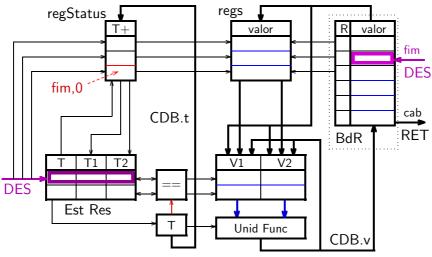

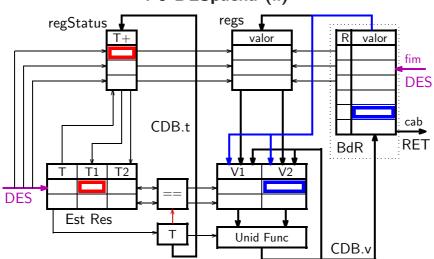

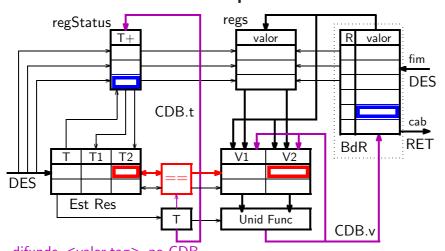

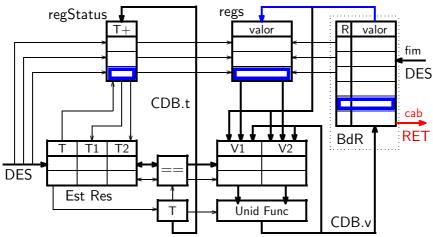

#### MIPS - microarquitetura

Microarquitetura = implementação do conjunto de instruções

Estrutura ↔como componentes são interligados Seqüenciamento ↔movimento de dados entre componentes

estrutura = datapath estática següenciador = controle dinâmico

HEPR Dinf RCC

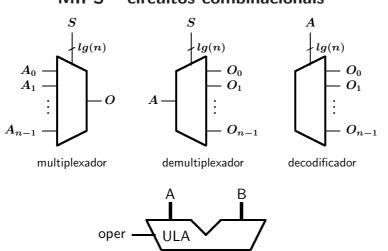

#### MIPS - circuitos combinacionais

2007-1

Arquitetura II — MIPS

HEPR Dinf RCC 96

stat Res

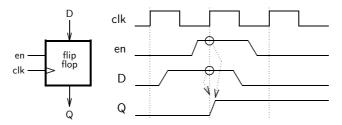

# MIPS – circuitos seqüenciais

TIEPR Dist RCC 07

Arquitetura II — MIPS 2007-1

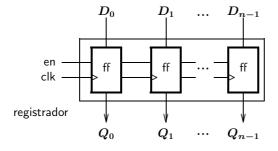

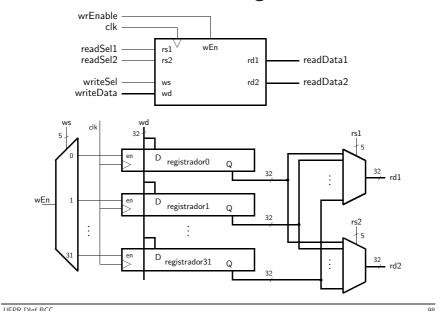

### MIPS - bloco de registradores

Arquitetura II — MIPS 2007-1

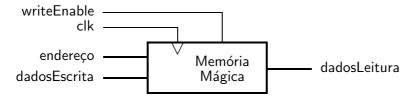

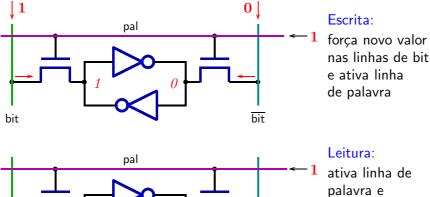

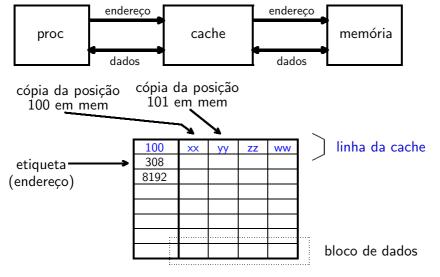

#### MIPS - memória idealizada

Modelo simplificado da memória

- leituras e escritas completam em 1 ciclo

- \* leitura pode ocorrer a qualquer instante (combinacional)

- \* escrita efetuada na borda ascendente do relógio escrita habilitada

- → dados e endereços estáveis na borda do relógio

- modelo mais realista será discutido adiante

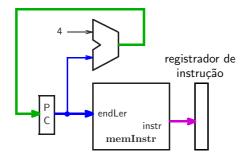

### MIPS - busca de instruções

- conteúdo do PC indexa memória

- ao final do ciclo

- \* nova instrução no Registrador de Instrução

- \* PC é incrementado

HEPR Dist RCC 100

Arquitetura II — MIPS 2007-1

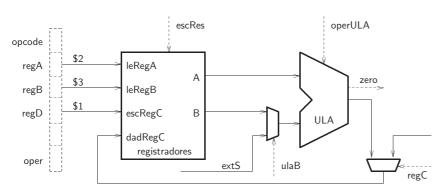

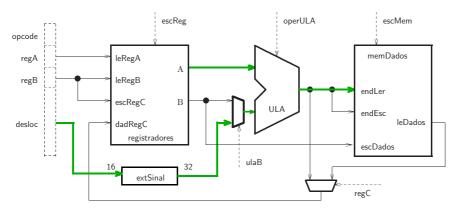

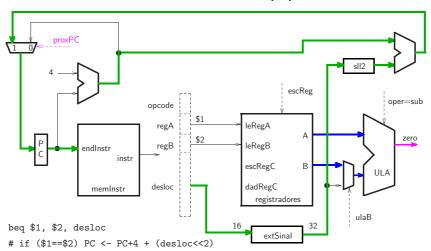

## MIPS - instruções de ALU (i)

add \$1, \$2, \$3 # \$1 <- \$2 + \$3

HEPR Dinf RCC 101

Arquitetura II — MIPS 2007-1

# MIPS - instruções de ALU (ii)

add \$1, \$2, \$3 # \$1 <- \$2 + \$3

## MIPS - instruções de ALU (iii)

add \$1, \$2, \$3 # \$1 <- \$2 + \$3

TIEPR DISF RCC 103

Arquitetura II — MIPS 2007-1

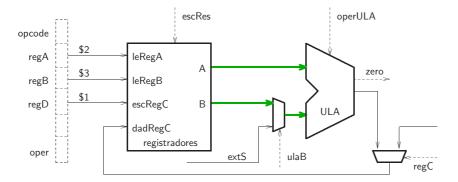

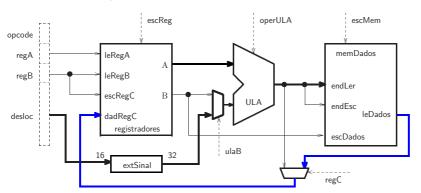

# MIPS - acesso à memória (i)

lw \$8, desloc(\$15) # \$8 <- M[desloc + \$15]

sw \$8, desloc(\$15) # M[desloc + \$15] <- \$8</pre>

HEPR Dinf RCC 10A

Arquitetura II — MIPS 2007-1

# MIPS - acesso à memória (ii)

lw \$8, desloc(\$15) # \$8 <- M[desloc + \$15]</pre>

### MIPS - acesso à memória (iii)

lw \$8, desloc(\$15) # \$8 <- M[desloc + \$15]</pre>

TIEPR DISF RCC 106

Arquitetura II — MIPS 2007-1

# MIPS - acesso à memória (iv)

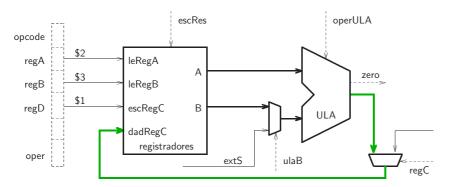

sw \$8, desloc(\$15) # M[desloc + \$15] <- \$8

HEPRING RCC 100

Arquitetura II — MIPS 2007-1

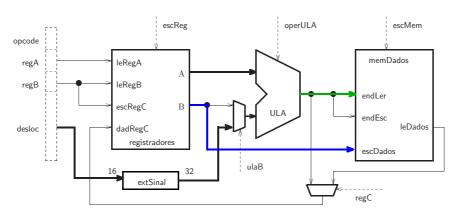

# MIPS - desvios (i)

Arquitetura II — MIPS 2007-1

# MIPS - desvios (ii)

HEPR Dist RCC 100

Arquitetura II — MIPS 2007-1

# MIPS - desvios (iii)

HEPR Dinf RCC 110

Arquitetura II — MIPS 2007-1

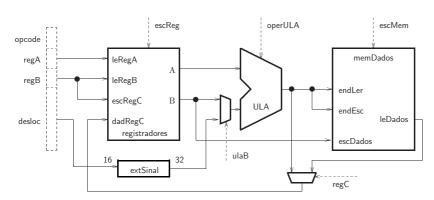

# MIPS - CPU completa

LIFPR Dinf RCC 111

#### MIPS - exercícios

Desenhe os diagramas completos do processador para executar as instruções:

- jump

- jump-and-link

- jump-register

- addi (add imediato)

HEPR Dist RCC 117

Arquitetura II — segmentação

2007-1

#### revisão: compiladores

- quem escreve um compilador deseja

- \* regularidade

- \* ortogonalidade

- \* composabilidade

- conjuntos de instruções ortogonais quanto a

- \* operações

- \* tipos de dados

- \* modos de endereçamento

- \* completude

uma, ou condições de desvio  $\Longrightarrow$  eq lt todas as soluções, condições de desvio  $\Longrightarrow$  eq ne lt gt le ge mas não algumas

HEPR DIM RCC 113

Arquitetura II — segmentação

2007-1

# Modelo sequencial

Conjunto de instruções de processadores "comuns" define um modelo seqüencial de execução:

cada instrução é completamente executada e altera o estado do processador antes do início da próxima instrução

Este modelo facilita muito a vida do programador!

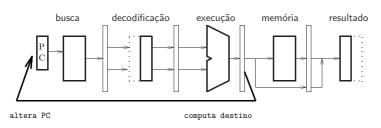

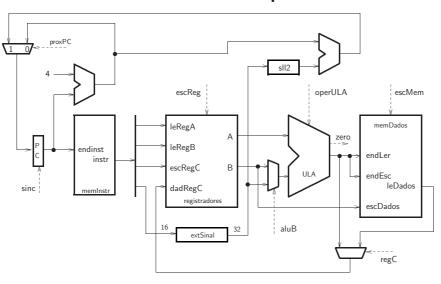

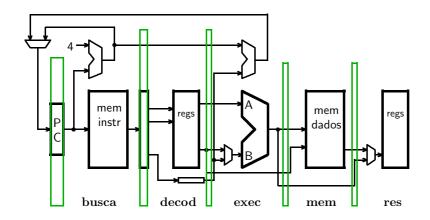

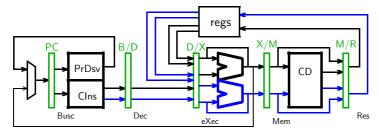

# Implementação mono-ciclo

- \* busca busca instrução que será executada

- \* decodificação decodifica instrução e acessa conteúdo dos registradores

- \* execução executa operação de ULA ou cálculo de endereço

- \* memória acesso à memória de dados

- \* resultado armazena resultado no bloco de registradores

HEPR Dist RCC 116

Arquitetura II — segmentação 2007-1

# Implementação multi-ciclo

Instrução completa em alguns ciclos de relógio: CPI>1

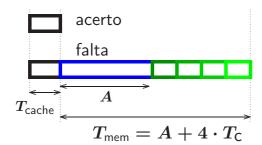

$$egin{array}{ll} T_{

m ciclo} & \geq & \max(T_{

m busca}\,, T_{

m decod}\,, T_{

m ex}\,, T_{

m mem}\,, T_{

m res}) \ & \geq & {f 5} \; {

m unidades} \; {

m de} \; {

m tempo} \end{array}$$

HEPR Dist RCC 116

Arquitetura II — segmentação 2007-1

# Implementação multi-ciclo

$$\mathsf{CPI} = \sum_{j=0}^{n} \mathsf{CPI}_{j} \times \mathsf{F}_{j}$$

$$\frac{\mathsf{instr}}{\mathsf{ALU}} \quad \begin{array}{c} \mathsf{freq}[\%] \quad \mathsf{ciclos} \\ \mathsf{ALU} \quad \quad 40 \quad 4 \\ \mathsf{load} \quad \quad 25 \quad 5 \\ \mathsf{store} \quad \quad 10 \quad 4 \\ \mathsf{desvios} \quad \quad 25 \quad 4 \\ \hline \quad \quad \quad \mathsf{CPI} \quad 4.25 \\ \end{array}$$

IIFPR Dinf RCC 117

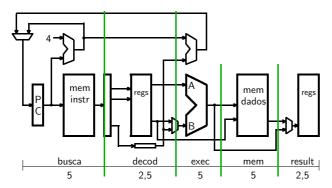

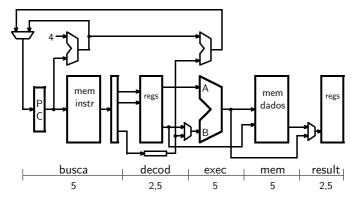

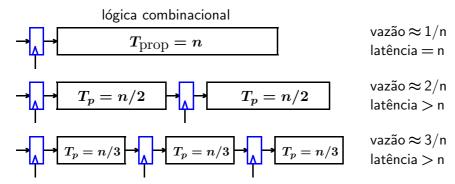

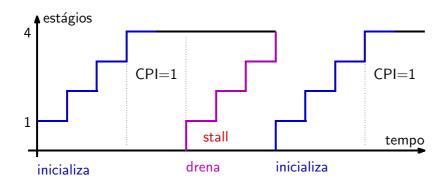

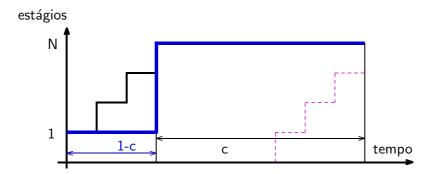

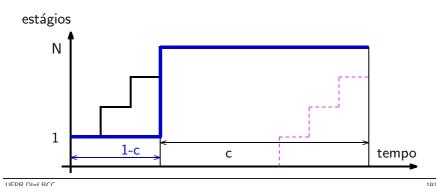

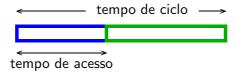

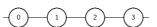

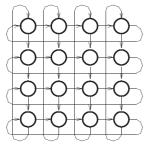

# Segmentação

- Segmentação: adicionar registradores entre unidades funcionais

- vazão é proporcional ao número de estágios

- latência aumenta por causa dos registradores

HEPR Dist RCC 11

Arquitetura II — segmentação 2007-1

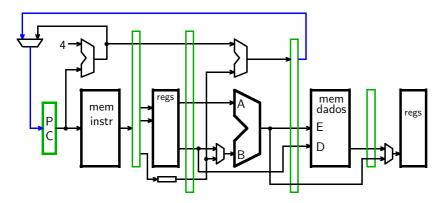

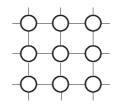

# Implementação com segmentos

HEPR DIM RCC 110

Arquitetura II — segmentação 2007-1

# Implementação com segmentos - controle

LIEPR Dinf RCC 120

#### Segmentação

- Circuito de dados

- \* componentes diversos com tempos de propagação distintos

- \* instruções usam mais componentes que os disponíveis

- ⇒ riscos estruturais

structural hazards

- dependências de dados entre instruções nos diversos estágios

- \* ∃ dependências entre instruções nos estágios

- ⇒ dependências de dados

data dependencies

- o escalonamento de instruções pode ser afetado por instruções nos outros estágios

- \* ∃ relacionamento entre instruções nos estágios

- ⇒ dependências de controle

control dependencies

LIEPR Dinf BCC

Arquitetura II — segmentação

2007-1

# Desempenho da segmentação

$$\mathsf{ganho} \ = \ \frac{\mathsf{CPI} \ \mathsf{sem} \ \mathsf{pipeline}}{\mathsf{CPI} \ \mathsf{com} \ \mathsf{pipeline}} \times \frac{\mathsf{ciclo} \ \mathsf{sem} \ \mathsf{pipeline}}{\mathsf{ciclo} \ \mathsf{com} \ \mathsf{pipeline}}$$

HEPR Dinf RCC

122

Arquitetura II — segmentação

2007-1

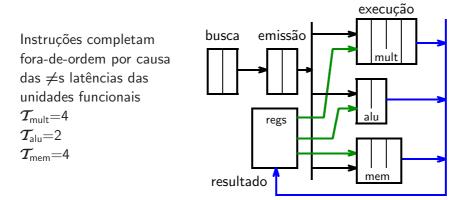

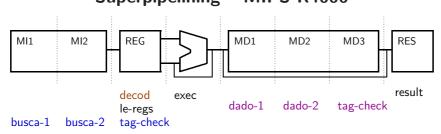

# Desempenho da segmentação (cont.)

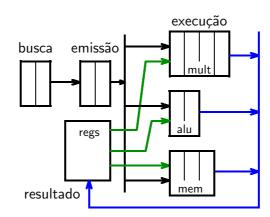

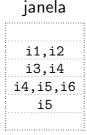

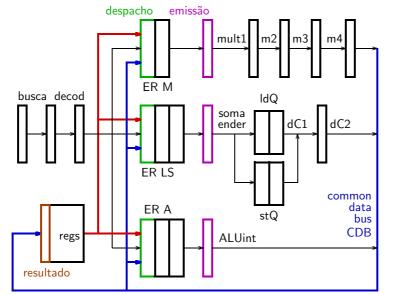

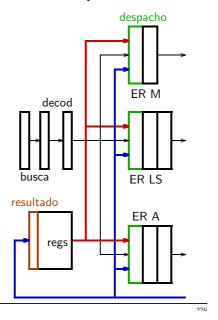

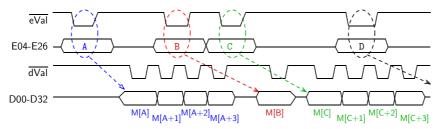

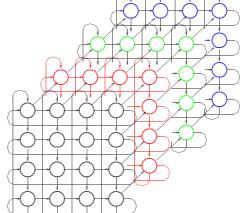

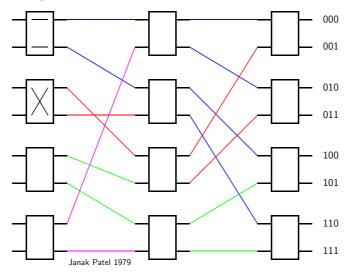

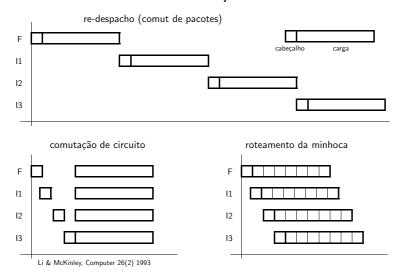

# Tipos de processadores segmentados linear busca decod exec mem res busca emissão execução regs regs regs tipo Diagrací

#### Pipeline não-linear

2007-1

Arquitetura II - segmentação

Barramento de resultado deve ser reservado quando instrução é emitida para execução (reg de deslocamento) → se barramento estará ocupado, segura execução

HEPR Dinf RCC 12

Arquitetura II — segmentação 2007-1

# Riscos com segmentação

Riscos são condições que levam a comportamento incorreto se medidas apropriadas não forem tomadas

• Riscos estruturais structural hazards

\* quando duas instruções **diferentes** necessitam do **mesmo** recurso no **mesmo** ciclo

• riscos com dados data hazards

- \* quando duas instruções **diferentes** usam **mesmo** local de armazenamento;

- \* resolução do risco deve garantir aparência de que instruções executaram na ordem seqüencial correta

- riscos de controle control hazards

- \* quando uma instrução determina **quais** instruções serão executadas a seguir (desvios, saltos, funções)

# Riscos com segmentação

Riscos

Arquitetura II - segmentação

- \* potenciais violações de dependências no programa

- \* implementação deve garantir que dependências não são violadas

- Resolução de riscos

- \* estática: compilador/programador garante corretude

- \* dinâmica: hardware verifica conflitos em tempo de execução

- Inter-travamentos no pipeline

interlocks

- \* mecanismo para resolução dinâmica de riscos

- \* deve detectar e resolver dependências em tempo de execução

HEDR Dief RCC 10

# Riscos estruturais

- Duas instruções diferentes necessitam do mesmo recurso no mesmo ciclo

- \* exemplo: processador em que loads e stores usam mesma porta de memória que busca de instruções

- \* nenhuma instrução completa no oitavo ciclo (bolha)

- \* Arquitetura Harvard versus Arquitetura Princeton

HEPR Dinf RCC 128

Arquitetura II — segmentação 2007-1

#### Resolução de riscos estruturais

Riscos estruturais podem ser reduzidos se:

- cada instrução usa recurso somente uma vez,

- sempre no mesmo estágio, e

- durante um ciclo.

- RISCs são projetados para satisfazer estes requisitos:

- ightharpoonup por causa do pipeline, memória deve ser capaz de atender  $\geq 1$  requisição/ciclo 1 instr/ciclo + 1/4 ld-st/ciclo

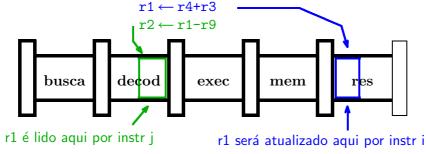

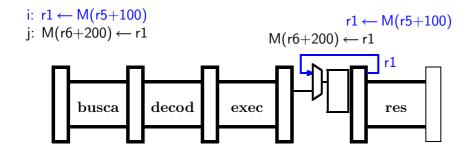

#### Riscos com dados

#### DATA HAZARDS:

# Quando duas instruções **diferentes** usam **mesmo** local de armazenamento

Deve parecer que instruções executam na ordem següencial correta

```

i: r1 ← r4 + r5

j: r2 ← r1 - r9  r1 foi produzido por i

k: r1 ← r6 ⊕ r3  valor de r1 em i é sobre-escrito resultado de i;j;k é o mesmo que i;k;j?

```

Convenção: **nome do risco** é a ordem do programa que **deve ser preservada pela implementação** (segment, superescalar)

HEPR Disf RCC 120

Arquitetura II — segmentação 2007-1

#### Riscos com dados - RAW

• Read-After-Write (RAW) instr **j** tenta ler operando r1 ANTES que instr **i** escreva resultado

i:

$$r1 \leftarrow r4 + r3$$

j:  $r2 \leftarrow r1 - r9$

Risco decorre de uma dependência de dados, causada pela comunicação entre as duas instruções add e sub através de r1

HEPR Dinf RCC

#### Riscos com dados - WAR

2007-1

Write-After-Read (WAR)

instr j escreve operando em r2 ANTES que instr i leia-o

i:

$$r4 \leftarrow r2 + r3$$

j:  $r2 \leftarrow r1 - r9$

Arquitetura II - segmentação

- Risco decorre de uma anti-dependência dependência artificial causada pelo re-uso do nome r2

- anti-dependências não ocorrem num pipeline linear de 5 estágios:

- ⊳ leituras ocorrem sempre no estágio 2 (decod)

- ⊳ escritas ocorrem sempre no estágio 5 (result)

- → MAS anti-dependências ocorrem em pipelines não-lineares p.ex CRAY e super-escalares

#### Riscos com dados - WAW

• Write-After-Write (WAW) instr **j** escreve operando em r3 ANTES que instr **i** escreva-o

i:

$$r3 \leftarrow r4 + r5$$

j:  $r3 \leftarrow r8 - r9$

- Risco decorre de uma dependência de saída dependência artificial causada pelo re-uso do nome r3

- dependências de saída não ocorrem num pipeline linear de 5 estágios

- ⊳ escritas em regs ocorrem somente no estágio 5 (result)

- ⊳ MAS dependências de saída ocorrem em pipelines não-lineares

- Read-After-Read (RAR) não é risco

HEPR Dinf RCC 133

Arquitetura II — segmentação 2007-1

# Dependências e riscos

**dependências** são características do programa o programador escreveu o código numa certa ordem

**riscos** decorrem de características da implementação o projetista do processador escolheu truques "perigosos"

HEPR Dinf RCC

Arquitetura II — segmentação 2007-1

# Solução simples para RAW (parcial)

- Circuito detecta risco, e então insere bolha:

atrasa instrução j até ocorrer escrita do resultado de i

- \* solução simples segura instrução dependente na busca

- \* desempenho ruim por causa dos ciclos desperdiçados

i:  $r1 \leftarrow r2+r3$  B D Ex M R j:  $r2 \leftarrow r1-r9$  B \*\* \*\* D Ex M F

stall

solução pressupõe que, em cada ciclo, registradores são atualizados e então são lidos

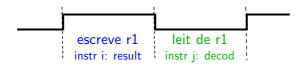

# Controle de atrasos (stalls)

- Compara com estágios posteriores

- \* if (rs1(decod)==rd(exec) || rs1(decod)==rd(mem)) { bolha }

- ★ mesmo para rs2

- ★ nem todos conflitos são riscos: st não escreve reg, addi não lê reg...

Arquitetura II — segmentação

2007-1

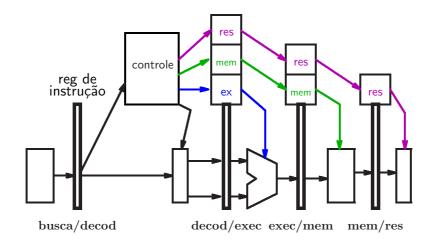

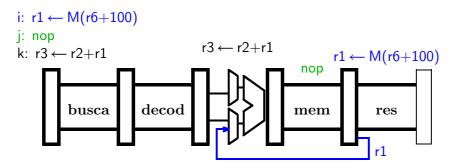

#### **Adiantamento**

Ao invés de atrasar, adianta resultado para entradas da ULA: usa controle de atrasos para decidir se deve adiantar, e usa multiplexadores para escolher fonte do resultado.

Adiantamento = forwarding, bypassing, short-circuiting

HEPR Dinf RCC 12:

Arquitetura II — segmentação 2007-1

#### **Adiantamento**

Adiantamento para o estágio de memória load seguido de store

LIEPR Dinf RCC 138

#### **Adiantamento**

Adiantamento para o estágio de memória: load seguido por add

- Risco deve ser detectado por hardware e bolha inserida (nop)

- \* desempenho cai por causa da bolha

- Compilador deve tentar preencher bolha com instrução "boa"

- ★ load delay slot usado no CdI MIPS-I e eliminado em MIPS-II por que?

HEPR Dist RCC 130

Arquitetura II — segmentação

# Adiantamento - circuito completo

2007-1

HEPR Dist RCC

Arquitetura II — segmentação 2007-1

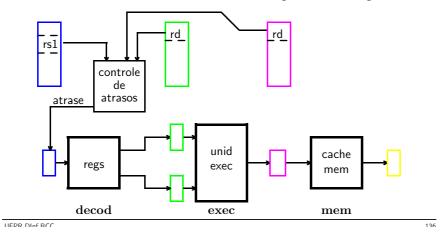

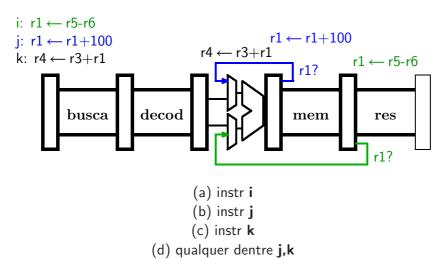

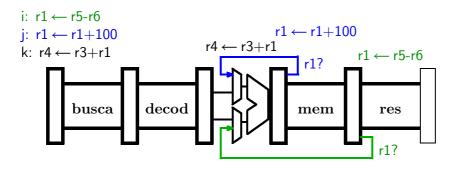

# Pergunta:

Quem fornece r1 para instrução k?

LIEPR Dinf RCC

# Resposta:

Quem fornece r1 para instrução k?

(a) instr i

(b) instr j é a que mantém a ordem seqüencial

(c) instr k

(d) qualquer dentre j,k

HEPR Dist RCC 1.

Arquitetura II — segmentação 2007-1

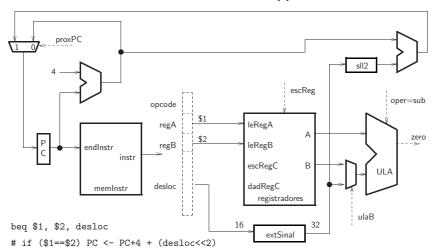

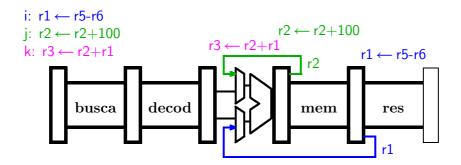

#### Riscos de Controle

Quando uma instrução determina **quais** instruções serão executadas a seguir (desvios, saltos, funções)

Desvio é efetuado em **mem**, após comparação na ULA ⇒ as instruções no caminho não-tomado devem ser anuladas

HEPR Dinf RCC 14

2007-1

Riscos de Controle

|      |              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9       |

|------|--------------|---|---|---|---|---|---|---|---|---------|

| i:   | beq r1,r0,8  | В | D | Е | М | R |   |   |   |         |

| i+1: | sub r2,r8,r9 |   | В | D | Ε | * | * |   |   | anulada |

| i+2: | lw rx, C(ry) |   |   | В | D | * | * | * |   | anulada |

| i+3: | sw ri,D(rj)  |   |   |   | В | * | * | * | * | anulada |

| i+8: | add r3,r4,r5 |   |   |   |   | В | D | Ε | Μ | R       |

| i+9: | add r6,r7,r8 |   |   |   |   |   | В | D | Ε | B R     |

Se CPI=1, 30% das instruções são desvios, penalidade de 3 ciclos  $\Longrightarrow$  CPI<sub>novo</sub>=1.9

• Desempenho pode ser melhorado:

Arquitetura II — segmentação

- \* descobre direção antes: compara com zero em decod

- \* computa endereço de destino: adiciona somador em decod

- → penalidade de UM ciclo ao invés de três

#### Riscos de Controle

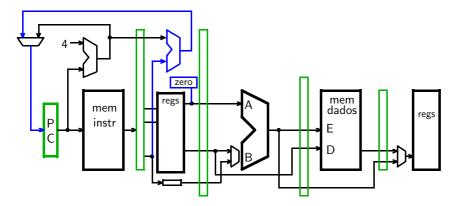

Desvio é efetuado em **decod**, após comparação com ZERO

Se CPI=1, 30% das instruções são desvios, penalidade de 1 ciclo  $\Longrightarrow$  CPI<sub>novo</sub>=1.3

LIEPR Dinf BCC

Arquitetura II — segmentação 2007-1

#### Tratamento de Riscos de Controle

- Tratamento de riscos de controle é MUITO importante pelo impacto no desempenho

- \* de 1/3 a 1/6 de todas instruções são desvios

- \* penalidade de um, dois ou três ciclos

- \* pipelines com mais estágios \iff desempenho pior

- Atrasa instruções até decidir se desvia

- Previsão de desvios → prever direção do desvio

- \* reduz/elimina penalidade se previsão correta

- \* pode aumentar penalidade quando erra

- \* Técnicas:

previsão estática - segue sempre mesmo caminho previsão dinâmica - depende do comportamento do programa

HEPR Dinf RCC

Arquitetura II — segmentação 2007-1

#### Previsão de desvios

#### • Previsão Estática

⊳ prevê sempre não-tomado MIPS, SPEC95,  $\approx 40\%$ MIPS, SPEC95,  $\approx 60\%$

⊳ prevê sempre tomado

⊳ prevê que para-trás é tomado

> previsão associada a opcodes

delayed branches

• Previsão dinâmica

⊳ será visto mais tarde

#### **Desvios Atrasados**

Sempre executa a próxima instrução

OK com pipelines simples

i:  $PC \leftarrow PC+8 \text{ if } r1 == 0$

i+1: r2 ← r8 - r9 sempre é executada

. . .

i+8:  $r3 \leftarrow r4 + r5$

- É necessário que branch delay slot seja preenchido

- ⊳ preenche com instrução antes do desvio (i-1)

- ▶ preenche com instrução de destino

- \* SE é seguro executar instrução de destino

- \* ajuda somente no caso do desvio tomado

- ⊳ preenche com instrução após o desvio (i+2)

- \* SE é seguro executar instrução após o desvio

- \* ajuda somente no caso do desvio não-tomado

HEPR Dist RCC 12

Arquitetura II — segmentação

2007-1

## **Desvios Atrasados**, Loads Atrasados

Arquiteturas que expõem riscos do pipeline ao software, como nos casos de *delayed load*s e *branch delay slot*s resultam em programas com número significativo de nops inseridos pelo compilador.

Estas soluções misturam arquitetura (ISA) com implementação (pipeline linear)

Isso é uma má idéia©

HEPR Dist RCC

Arquitetura II — desvios e excessões

2007-1

#### resumo - Riscos de Controle

- Riscos de controle tem efeito devastador no desempenho

- Mecanismos simples de previsão de desvios:

- ★ segura fluxo até decidir direção do desvio (penalidade 1-2 ciclos)

- ★ prediz que desvio é sempre não-tomado (penalidade 1 ciclo, ≈40% das vezes)

- ★ prediz que desvio é sempre tomado (penalidade 1 ciclo, ≈60% das vezes)

- desvio atrasado "esconde" penalidade quando desvio não-tomado

- \* ocupar o espaço pode ser difícil

- $\star$  mistura arquitetura com implementação

HEPR Dinf RCC 15(

#### revisão - Riscos

• modelo seqüencial de execução:

cada instrução é completamente executada e altera o estado do processador antes do início da próxima instrução

- Riscos são potenciais violações de dependências no programa

- implementação deve garantir que dependências não são violadas

- Resolução de riscos:

- \* estática: compilador/programador garante corretude

- \* dinâmica: hardware verifica conflitos em tempo de execução

- Inter-travamento no pipeline

interlocks

2007-1

- \* mecanismo para resolução dinâmica de riscos

- \* deve detectar e resolver dependências em tempo de execução

HEPR Dinf RCC

Arquitetura II — desvios e excessões

2007-1

#### mais revisão - Riscos

• Risco estrutural

structural hazards

- Risco de dados

data hazards

- duas instruções diferentes usam mesmo local de armazenamento

- aparência de execução na ordem següencial correta

- Risco de controle

control (flow) hazards

□ uma instrução determina quais instruções serão executadas a seguir (desvios, saltos, funções) pior impacto no desempenho

HEPR Dinf RCC 15

Arquitetura II — desvios e excessões

2007-1

#### Dependências de Controle

- Desempenho dos processadores é limitado pelos desvios

- Maioria das dependências de dados podem ser eliminadas pelo compilador + adiantamento;

- Dependências de controle não podem ser eliminadas por causa do comportamento dinâmico dos programas...

- Regra dos 85/60: medições indicam que aproximadamente

- \* 85% dos desvios "para trás" são tomados

- \* 60% dos desvios "para frente" são tomados

- solução: adivinhar destino do desvio para antecipar a busca da próxima instrução porque fazer alguma coisa é melhor que não fazer nada

#### Riscos de controle e previsão de desvios

#### Previsão Dinâmica de Desvios

- Passado recente pode auxiliar a prever futuro próximo: usar a história dinâmica dos desvios para prever sua direção

- \* se desvio será tomado ou não-tomado

- \* qual o endereço de destino

- porque é dinâmico, previsor pode se ajustar a

- \* fases distintas da execução do programa

- \* comportamento de desvios específicos

HEPR Dist RCC 154

Arquitetura II — desvios e excessões

2007-1

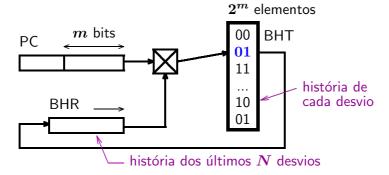

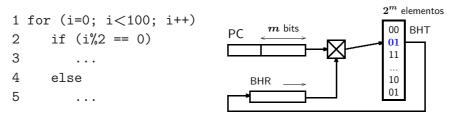

#### Previsão Dinâmica de Desvios

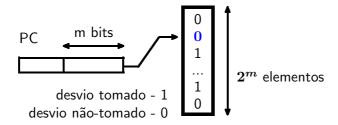

Tabela com  $\mathbf{2}^m$  bits no estágio de busca

- acessa tabela com m bits do PC

- \* tabela contém 1 se desvio foi tomado na última execução

- st tabela contém  $oldsymbol{0}$  se desvio não foi tomado na última execução

- prevê que nesta execução tomará mesmo caminho que na anterior

- atualiza o bit quando errar a previsão

HEPR Dist RCC 155

Arquitetura II — desvios e excessões

2007-1

#### Previsão Dinâmica de Desvios

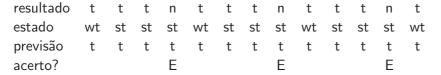

Exemplo: loop executa três voltas e então prossegue:

Na previsão com um bit, ocorrem duas previsões erradas a cada mudança c.r.a história recente

resultado t t t n t t t n t t t n t t previsão t t t T N t t T N t t T N acerto?

Com este método são duas as previsões erradas a cada vez que seqüência muda...

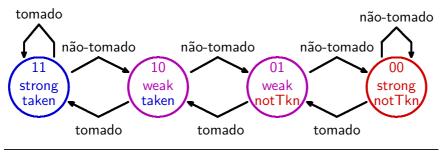

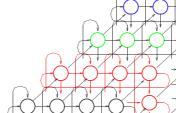

#### Previsores melhores: contadores de 2 bits

Contador de dois bits implementa histerese e melhora previsão:

Previsões erradas caem para a metade.

HEPR Dist RCC 15

Arquitetura II — desvios e excessões

2007-1

#### Previsores melhores: correlação de previsões

Desvios em instruções distintas podem ser relacionados:

if

$$(a < 0) a = 0$$

;

if  $(b > 0) b = 0$ ;

if  $(a != b) \{ ... \}$

Se as duas primeiras condições são verdadeiras, a terceira será falsa; portanto a idéia é:

- manter história de todos os desvios recentes

história aproxima caminho seguido pelo programa

- Branch History Register (BHR) é um registrador de deslocamento que mantém resultado dos últimos N desvios

- PC e BHR são combinados para acessar tabela de previsão

- taxas de acerto ficam entre 80% e 90%

HEPRING 153

Arquitetura II — desvios e excessões

2007-1

# Previsores melhores: correlação de previsões

Apontador para tabela de previsão é uma combinação dos conteúdos do PC e do *Branch History Register* soma, sobreposição, ou concatenação

Gshare: um BHR de m-bits, ou-exclusivo do BHR com PC

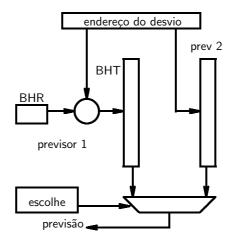

# Previsores ainda melhores: mais de um previsor

Desvios tem comportamentos distintos

→ usar previsores diferentes em desvios diferentes.

#### escolha:

se previsor escolhido errou e outro acertou inverte escolha

previsores híbridos, competitivos (tournament)

Gshare + contador de 2 bits

HEPR Dist RCC 160

Arquitetura II — desvios e excessões

2007-1

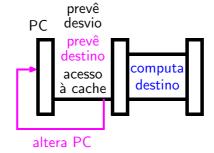

# Previsão de endereço de destino

Tabela de endereços de destino (Branch Target Buffer [BTB])

permite prever endereço de destino

se acerta previsão, evita inserção de bolha no pipeline

HEPR Dist RCC

Arquitetura II — desvios e excessões

2007-1

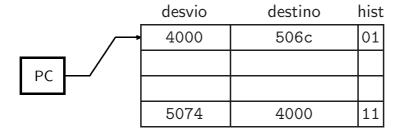

#### Tabela de endereços de destino

A tabela de endereços de destino é uma cache especial:

- índice e etiqueta são comparados com endereço da instrução de desvio

- conteúdo do BTB é o endereço de destino (cache de destinos)

- bits de previsão mantidos junto com endereço de destino

- geralmente associado à cache de instruções

# **Branch Target Cache:**

- \* armazena instrução de destino junto com endereço

- \* permite eliminar o desvio do fluxo de instruções branch folding

#### Tabela de endereços de destino

HEPR Dist RCC 163

Arquitetura II — desvios e excessões

2007-1

# Tabela de endereços de destino

Administração da tabela:

- armazena desvios não-tomados?

- o que fazer quando inicia execução (tabela vazia)?

- o que fazer com conflitos na tabela (tabela cheia)?

- o que fazer quando errar a previsão?

- quanto custa (CPI) errar uma previsão?

HEPR Dinf RCC

Arquitetura II — desvios e excessões

2007-1

# Previsão de chamada e retorno de funções

- Destino de saltos indiretos para retorno de função (jr)

é muito difícil de prever

- \* uma função pode ter vários endereços de retorno estáticos e/ou dinâmicos

- Solução: implementar uma pilha de retorno de funções no estágio de busca do processador

- \* salva endereço de retorno na pilha instrução jal

- \* desempilha ao retornar e prevê destino instrução jr r31

- O quê fazer com saltos indiretos que ∉ à funções? instrução jr

#### Resumo de Previsão de Desvios

- Previsão é útil em pipelines simples

- é imprescindível em processadores super-escalares

- processadores modernos usam

- \* previsores sofisticados

- \* tabela de endereco de destino

- \* pilha de retorno de funções

HEPR Dist RCC 166

Arquitetura II — desvios e excessões

2007-1

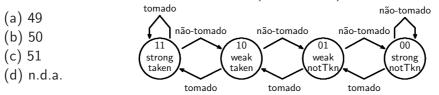

#### Pergunta:

Quantos erros de previsão na linha **2** para previsor BHR+BHT? BHT iniciaizado com 00 (não-tomado)

HEPR Dist RCC 16:

Arquitetura II — desvios e excessões 2007-1

#### Resposta:

Estados: 11-St 10-wt 01-wn 00-Sn

BHR com 8 bits, insere resultado na posição menos-significativa BHT com 256 posições, indexada com 8 bits do PC

PC = 0x200 (para simplificar), operação do PC com BHR é XOR Estruturas inicializadas com 0 em todas as posições

1 for(i=0; i<100; i++)

2 if (i%2 == 0)

3 ...

4 else

5 ...

quantos erros de previsão na linha 2?

OU

quantas voltas do laço para treinar

o previsor?

# Resposta: (cont)

```

pos BHT nova novoBHR

i dsv

BHR

acerto?

nt

0000.0000 0 00 -> 00 0000.0000 0

0

sim

1

t

0000.0000 0 00 -> 01 0000.0001 1

não

2

nt 0000.0001 1 00 -> 00 0000.0010 2

sim

3

0000.0010 2 00 -> 01 0000.0101 5

t

não

4

nt 0000.0101 5 00 -> 00 0000.1010 a

sim

5

0000.1010 a 00 -> 01 0001.0101 15

t

não

nt 0001.0101 15 00 -> 00 0010.1010 2a

6

7

0010.1010 2a 00 -> 01 0101.0101 55

não

nt 0101.0101 55 00 -> 00 1010.1010 aa

8

sim

1010.1010 aa 00 -> 01 0101.0101 55

9

não - 5 erros

10 nt 0101.0101 55 00 -> 00 1010.1010 aa

sim

1010.1010 aa 01 -> 10 0101.0101 55

11 t

sim <--acerto

```

HEPR Disf RCC 16

Arquitetura II — desvios e excessões

2007-1

# Interrompemos a nossa programação...

HEPR Dist RCC 117

# Arquitetura II — desvios e excessões

2007-1

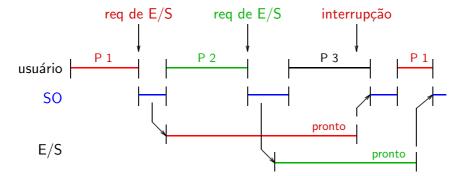

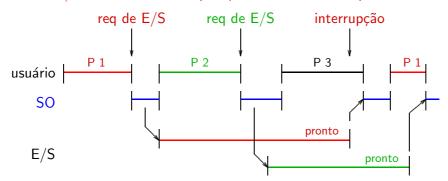

#### Interrupções e Excessões

- Interrupções

- \* geralmente com causa externa ao processador (assíncrona)

- \* não são relacionadas a uma instrução específica

- \* Exemplos: interrupção de dispositivo; falta de energia

- Excessões

- \* relacionadas à execução de uma instrução específica (síncrona)

- \* Exemplos: overflow, falta de página

- Traps

- \* relacionadas à execução de uma instrução específica

- \* rotina (hw+sw) de tratamento de excessões

2007-1

# **Eventos Síncronos vs Assíncronos**

- Síncrono evento relacionado com a seqüência de instruções ocorre durante a execução de uma instrução

- \* deve parar instrução que está executando correntemente

- \* falta de página durante instrução load ou store

- \* excessões aritméticas

- ★ chamadas de sistema (instruções trap ou syscall)

- Assíncrono evento sem relação com seqüência de instruções causada por um evento externo

- ★ desnecessário interromper instruções que estão executando

- ★ interrupções por dispositivos de E/S

- ★ interrupções por eventos catastróficos (erro na memória)

- Semi-síncrono

- ★ evento externo que pode interromper seqüência de instruções para garantir serviços (alta disponibilidade)

HEPR Dinf RCC 17

Arquitetura II — desvios e excessões 2007-1

#### Interrupções e Excessões – arquitetura

- Registrador de Interrupção

- \* vetor de bits indicando quais interrupções/excessões ocorreram

- Registrador de máscara

Arquitetura II - desvios e excessões

- \* vetor de bits indica quais inters/excessões estão desabilitadas

- \* escrever no registrador de máscara é instrução privilegiada

- \* alguns bits podem ser atualizados em modo usuário (overflow)

- \* algumas interrupções/excessões não são mascaráveis

HEPR Dist RCC 17

# Interrupções/Excessões Precisas

Uma interrupção ou excessão é considerada **precisa** se existe uma única instrução (ou ponto de interrupção) tal que todas as instruções anteriores àquela tenham alterado o estado, e nenhuma instrução após (e incluindo) aquela tenham modificado o estado.

Isso significa que a execução pode ser re-iniciada a partir do ponto de interrupção e resultados corretos serão produzidos.

Ver artigo de Smith & Pleszkun para soluções. IEEE-TC 37:5 1988

# Interrupções Precisas

- Interrupções Precisas facilitam MUITO o trabalho do SO na continuação do programa, ou na depuração

- Excessão/trap

- ⊳ todas instruções antes da causadora completam

- > nenhuma das instruções após a causadora completam

- ▶ instrução causadora ou completou ou não iniciou

- ▶ PC aponta instrução causadora

- Interrupção

- ⊳ Mesmo que excessão, mas ∄ instrução causadora

- ▶ Deve parecer que ocorreu entre duas instruções

- ▶ PC aponta para instrução que seria executada

HEPR Disf RCC 177

Arquitetura II — desvios e excessões

2007-1

# Tratamento de interrupções/traps

Quando ocorre interrupção/trap:

- efetua salto para rotina do SO

- \* vetor de tratadores, em geral amarrado no cj de instruções

- computa endereço de retorno

- salva informação de estado essencial

- \* PC

- \* CCs (condition codes)

- \* PSW (processor status word)

- ◆ troca modo de execução: usuário ⇒ sistema

HEPR DIM RCC 177

Arquitetura II — desvios e excessões

2007-1

#### Implementação de interrupções/traps

- Precisão é importante

- Interrupções e excessões simultâneas

- ▶ busca falta de página, referência desalinhada, protection fault

- ▶ decod instrução ilegal ou privilegiada

- ▶ exec excessões de aritmética (overflow, divisão por zero)

- ⊳ mem falta de página, referência desalinhada, protection fault

- ▶ res nenhuma

# Falta de Página

$\mathbf{B}$  $\mathbf{D}$  $\mathbf{E}\mathbf{x}$   $\mathbf{M}$   $\mathbf{R}$ falta de página (mem)  $\mathbf{B}$  $\mathbf{D}$  $\mathbf{E}\mathbf{x}$   $\mathbf{M}$  falta de página (busca)  $\mathbf{B}$  $\mathbf{D}$  $\mathbf{E}\mathbf{x}$   $\mathbf{M}$  anulada  $\mathbf{B}$ D Ex M R anulada  $\mathbf{B}$ Ex M R 🗕 anulada salta para tratador

início do tratador  $\longrightarrow$  B D Ex M R

- Instrução anterior completou res//mem

- anula todas instruções subseqüentes

- impede que instrução causadora altere estado (se for load)

Arquitetura II — desvios e excessões

LIEPR Dinf BCC

#### 2007-1

#### Excessão de Aritmética

Ex M R  $\mathbf{B}$  $\mathbf{D}$  $\mathbf{B}$ D  $\mathbf{E}\mathbf{x} \mathbf{M} \mathbf{R}$  excessão (exec)  $\mathbf{B}$ Ex M R  $\mathbf{B}$  $\mathbf{D}$  $\mathbf{E}\mathbf{x} \mathbf{M} \mathbf{R}$ anulada  $\mathbf{B}$  $\mathbf{D}$  $\mathbf{E}\mathbf{x} \ \mathbf{M}$ anulada salta para tratador

início do tratador B D Ex M R

- Instruções anteriores podem completar

- anula todas instruções subseqüentes

HEPR Dist RCC 17

Arquitetura II — desvios e excessões

#### 2007-1

#### Excessões Múltiplas

falta de página instrução ilegal falta de página overflow

| usca | decod | exec  | mem   | result |        | _      |        |

|------|-------|-------|-------|--------|--------|--------|--------|

|      | busca | decod | exec  | mem    | result |        |        |

| •    |       | busca | decod | exec   | mem    | result |        |

|      |       |       | busca | decod  | exec   | mem    | result |

- Pipeline pode resolver

- \* estado c.r.a excessões passa pelos estágios junto com instrução

- \* mantém valor do PC junto a cada instrução

- \* não trata excessão até instrução chegar a result

- Interrupção é detectada na busca e instrução NOP é inserida

- Quando instrução chega a result

- \* salva PC $\longrightarrow$  EPC; endereço do vetor de interrupções  $\longrightarrow$  PC

- \* transforma instruções nos outros estágios em NOPs

# Complicações no Conjunto de Instruções

- Estado espalhado em vários recursos (CCs)

- Atualização antes de **mem/res** (auto-incremento)

- Instruções que completam fora de ordem

- \* outros mecanismos serão estudados adiante

- Interrupções ocorrem a qualquer momento

- O caso frequente não é o único/mais importante

- \* Desempenho não é o parâmetro mais crítico