Exemplo - Processos e Eventos

Codigo: example_process.tar.gz

Codigo em VHDL

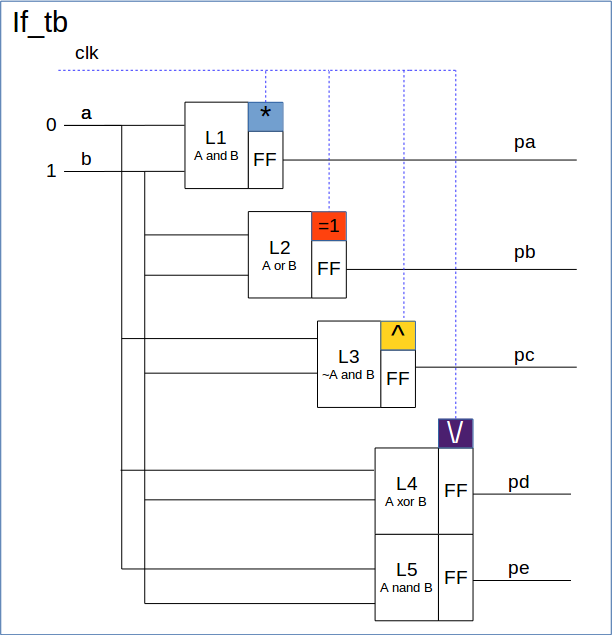

--== Header ============================================================================= library IEEE; use IEEE.std_logic_1164.all; ----------------------------------------------------------------------------------------- --== Entidade =========================================================================== ENTITY Process_tb IS END Process_tb; ----------------------------------------------------------------------------------------- --== Arquitetura ======================================================================== ARCHITECTURE behavior OF Process_tb IS -- Sinais Locais signal a : std_logic; signal b : std_logic; signal pa : std_logic; signal pb : std_logic; signal pc : std_logic; signal pd : std_logic; signal pe : std_logic; signal clk : std_logic; -- Comportamento BEGIN a <= '0'; b <= '1'; process(clk) begin pa <= a and b; -- L1 if clk = '1' then pb <= a or b; -- L2 end if; if rising_edge(clk) then pc <= (not a) and b; -- L3 end if; if falling_edge(clk) then pd <= a xor b; -- L4 pe <= a nand b; -- L5 end if; end process; -- Nao considerar esta parte clk_process: process begin clk <= '0'; wait for 1 ns; clk <= '1'; wait for 1 ns; end process; END; -----------------------------------------------------------------------------------------

Circuito Compilado